PEOPLE'S DEMOCRATIC REPUBLIC OF ALGERIA

MINISTRY OF HIGHER EDUCATION AND

SCIENTIFIC RESEARCH

Mohamed Boudiaf University - M'sila

FACULTY OF TECHNOLOGY

DEPARTMENT OF ELECTRICAL ENGINEERING

Serial number.....

Registration number.....

Thesis Presented for graduation from LMD DOCTORATE

Major : Electromechanical

Specialty : Electromechanical

THEME

**Commandes avancées d'un système de production décentralisée photovoltaïque à base de convertisseurs parallèles à quatre bras**

Presented by

**AL-DWA Ala Addin Mohammed Mohammed Hussin**

Defended on:

In front of the Thesis committee member composed of:

| Last Name & First Name  | Grade     | Establishment               | Quality           |

|-------------------------|-----------|-----------------------------|-------------------|

| BERRABEH Fouad          | Professor | Univ. of M'sila             | Chairman          |

| CHEBABHI Ali            | Professor | Univ. of M'sila             | Supervisor        |

| CHOUDER Adel            | MCB       | Univ. of Bordj Bou Arreridj | Supervisor        |

| BENKHORIS Mohamed Fouad | Professor | Polytech Nantes, France     | External Examiner |

| ZEGHLACHE Samir         | Professor | Univ. of M'sila             | Internal Examiner |

| DJERIOU Salim           | MCA       | Univ. of M'sila             | Internal Examiner |

| REKIOUA Toufik          | Professor | Univ. of M'sila             | Invited           |

## **CERTIFICATE OF ORIGINAL AUTHORSHIP**

I, AL-DWA Ala Addin Mohammed Mohammed Hussin, declare that this thesis is submitted in fulfillment of the requirements for the award of Doctor of Philosophy in the Faculty of Technology at the University of M'sila.

This thesis is wholly my own work unless otherwise referenced or acknowledged. In addition, I certify that all information sources and literature used are indicated in the thesis. I also certify that the work in this thesis has not previously been submitted for a degree, nor has it been submitted as part of the requirements for a degree except as fully acknowledged within the text.

This research is supported by the University Training Research Projects titled Commande intelligents d'un système de production décentralisé photovoltaïque dans les réseaux électriques quatre fils à base de convertisseurs quatre bras avec tolérance aux pannes under the matriculation A01L07UN280120220005/2022.

Signature: AL-DWA Ala Addin Mohammed Mohammed Hussin

Date : 17/10/2025

## ACKNOWLEDGEMENTS

I would like to express my heartfelt gratitude and sincere appreciation to all those who have played a significant role in the completion of my Ph.D. thesis.

First and foremost, I am deeply grateful to my family for their unwavering support and understanding. I thank my **dear father** and my **beloved mother**, may God have mercy on her, for instilling in me a love of knowledge and for constantly encouraging me to pursue my dreams. I am also profoundly thankful to my beloved wife and my wonderful son, **Yazan**, for their patience, understanding, and sacrifices throughout this challenging journey. Your unwavering faith in me has been my constant source of inspiration.

I would like to extend special thanks to my brother, **Abdellah**, for his exceptional support and assistance throughout my studies. Your readiness to help, valuable insights, and constant encouragement have been instrumental in shaping the direction of my research and in helping me persevere through both the highs and lows of this journey.

My deepest gratitude goes to my supervisor, Professor **CHEBABHI Ali**, for your invaluable guidance, expertise, and continuous support throughout this work. Your insightful feedback and constructive criticism have constantly challenged me to improve and strive for excellence.

I am equally indebted to my co-supervisors, Professor **BARKET Said** and Dr. **CHOUDER Adel**, whose extensive knowledge, guidance, and valuable contributions have greatly enriched my research and broadened my understanding of the subject matter. I am truly grateful for the time and effort you devoted to mentoring and advising me, which has had a profound impact on the quality of my work.

I would also like to express my sincere appreciation to the members of the thesis jury committee, each by its name and its position, for accepting the invitation to evaluate and discuss my Ph.D. work. Your time, attention, and valuable comments are deeply appreciated.

Finally, to all those mentioned above, and to those who may not be explicitly named, please accept my heartfelt thanks. Without your support, this achievement would not have been possible. Thank you for being an integral part of my academic journey and for your unwavering belief in my abilities.

## Abstract :

In recent years, the integration of decentralized generation based on photovoltaic energy sources and static power converters has significantly increased, particularly in three-wire power networks. This trend supports the use of local energy resources near consumption points.

The photovoltaic-grid system is considered a promising solution to increase the share of renewable energy and enhance power quality within electrical networks. However, such systems are highly sensitive to variations in load or source parameters and power levels, which can impact their stability, synchronization, and energy quality. These technical challenges raise concerns about the reliability of decentralized generation systems.

This research primarily aims to explore various topologies and control strategies for decentralized photovoltaic-grid systems. These systems utilize interleaved DC-DC converters and four-leg inverters to inject power and improve power quality in four-wire electrical networks.

To enable the integration of high-power decentralized generation into four-wire networks, the study also investigates the use of multilevel converters and parallel configurations of static power converters.

A key focus is on selective control strategies for decentralized photovoltaic-grid systems and on addressing the issue of circulating currents in parallel converter structures. Solutions will be proposed to optimize the number of active converters based on the power requirements of the four-wire network.

To further enhance the performance of decentralized photovoltaic-grid systems, advanced control techniques will be introduced. These include adaptive nonlinear control, 3D Space Vector Pulse Width Modulation (3DSVPWM), and intelligent control strategies. These methods have demonstrated effectiveness in maintaining stability, ensuring synchronization, improving power quality, and dealing with parameter and power variations from loads or energy sources.

## Keywords:

Photovoltaic system, Two-level four-leg inverter, Circulating current, Power quality, Advanced and intelligent control strategies.

## الملخص:

شهدت السنوات الأخيرة تزايداً ملحوظاً في دمج أنظمة التوليد اللامركزي المتعددة على مصادر الطاقة الشمسية الكهروضوئية ومحولات القدرة الساكنة، خاصة في الشبكات الكهربائية ثلاثة الأسلام، مما يتيح الاستفادة من الموارد المحلية القريبة من أماكن الاستهلاك.

تعد أنظمة الربط بين الطاقة الشمسية والشبكة الكهربائية من البديل الواعدة لزيادة الطاقة المتجدددة وتحسين جودة الطاقة في الشبكات الكهربائية. ومع ذلك، فإن استقرار هذه الأنظمة وترامنها وجودة الطاقة التي توفرها تتأثر بشكل كبير بتقلبات الأحوال أو مصادر الطاقة، مما يثير تحديات تقنية تتعلق بموثوقية أنظمة التوليد اللامركزي.

يركز هذا البحث على دراسة مختلف البنية الطبوولوجية واستراتيجيات التحكم لأنظمة التوليد اللامركزي الكهروضوئية المتصلة بالشبكة، والتي تعتمد على محولات DC-DC المتداخلة وعواكس رباعية الأذرع، بهدف تحسين جودة الطاقة وضخ القدرة في الشبكات الكهربائية رباعية الأسلام.

ولدمج التوليد اللامركزي في الشبكات رباعية الأسلام ذات القدرة العالية، يتناول البحث أيضاً استخدام المحولات متعددة المستويات، بالإضافة إلى البنية التي تعتمد على توصيل محولات القدرة الساكنة على التوازي.

سيتم تقديم استراتيجيات تحكم انتقائية لهذا النوع من الأنظمة، إلى جانب حلول لمشكلة التيار الدوارة في البنية المتوازية للمحولات، بهدف تحسين عدد المحولات العاملة بناءً على متطلبات القدرة في الشبكة رباعية الأسلام.

ولتطوير أداء هذه الأنظمة، سيتم تقديم تقييمات تحكم متقدمة مثل التحكم غير الخطبي التكيني، وتقنية تعديل عرض النبضة ثلاثة الأبعاد (3DSVPWM)، بالإضافة إلى تقييمات تحكم ذكية. وقد أثبتت هذه الطرق فعاليتها من حيث الاستقرار، والتزامن، وجودة الطاقة، وقدرتها على التعامل مع تقلبات الأحوال أو مصادر الطاقة.

## الكلمات المفتاحية

## Résumé :

Ces dernières années, l'intégration croissante de la production décentralisée basée sur des sources d'énergies photovoltaïques et des convertisseurs statiques est en forte progression pour les réseaux électriques à trois fils qui permettent l'exploitation des ressources locales proches des lieux de consommation.

Le système photovoltaïque-réseau électrique est une des alternatives envisagées pour augmenter le taux d'énergie renouvelable et d'améliorer la qualité de l'énergie dans les réseaux électriques. La stabilité, la synchronisation et la qualité de l'énergie d'un système photovoltaïque-réseau électrique est fortement sensible aux variations des paramètres et de puissance venant des charges ou des sources d'énergie. Toutefois, des contraintes techniques principalement liées à ces performances soulèvent des problèmes difficiles sur la fiabilité du système de production décentralisée.

Dans ce travail de recherche, l'objectif principal est d'aborder les différentes topologies et stratégies de commande des systèmes de productions décentralisées photovoltaïques-réseaux électriques basée sur des convertisseurs statiques de puissance DC-DC entrelacés et des onduleurs à quatre bras en vue d'injecter la puissance et d'améliorer la qualité de l'énergie dans les réseaux électriques à quatre fils.

Afin d'intégrer la production décentralisée dans les réseaux électriques à quatre fils de forte puissance, les systèmes de productions décentralisées photovoltaïques-réseaux électriques basée sur les convertisseurs multiniveaux et les structures mises en parallèle des convertisseurs statiques de puissance seront également abordées dans ce travail de recherche.

Une sélectivité dans la commande de ce type de système de production décentralisée photovoltaïque-réseaux électriques et une solution pour le problème du courant de circulation dans les structures mises en parallèle des convertisseurs statiques seront introduites, pour optimiser le nombre de convertisseurs statiques en service en fonction de la puissance de réseau électrique à quatre fils.

Pour améliorer les performances de ces systèmes de productions décentralisées photovoltaïques-réseaux électriques, des techniques de commande avancées seront introduites. Il s'agira de la commande non-linéaire adaptative, de la commande par 3DSVPW et d'autres commandes intelligentes. Ces commandes ont fait preuve d'efficacité du point de vue de la stabilité, de la synchronisation, de la qualité d'énergie et de la prise en compte du problème de la variation des paramètres et de puissance venant des charges ou des sources d'énergie.

## Mots clés :

Système photovoltaïque, Onduleur à quatre bras à deux niveaux, Courant de circulation, Qualité d'énergie, Commandes avancées et intelligentes.

## TABLE OF CONTENTS

|                                                                                                              |             |

|--------------------------------------------------------------------------------------------------------------|-------------|

| <b>CERTIFICATE OF ORIGINAL AUTHORSHIP</b>                                                                    | <b>ii</b>   |

| <b>ACKNOWLEDGEMENTS</b>                                                                                      | <b>iii</b>  |

| <b>Abstract</b>                                                                                              | <b>iv</b>   |

| <b>TABLE OF CONTENTS</b>                                                                                     | <b>vi</b>   |

| <b>List of Abbreviations</b>                                                                                 | <b>x</b>    |

| <b>List of Figures</b>                                                                                       | <b>xiii</b> |

| <b>List of Tables</b>                                                                                        | <b>xv</b>   |

| <b>Publications and communications under this Phd Thesis</b>                                                 | <b>xvi</b>  |

| <b>Chapter 1: Overview of PV Systems for Grid-Connected Application and Power Quality Improvement</b>        |             |

| I.1. Introduction                                                                                            | 7           |

| I.2. Overview of Semiconductors                                                                              | 8           |

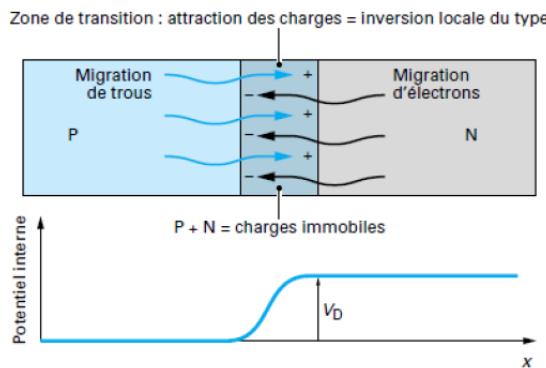

| I.2.1. Structure of a PN Diode                                                                               | 8           |

| I.2.2. I-V Characteristics of the PN Diode                                                                   | 8           |

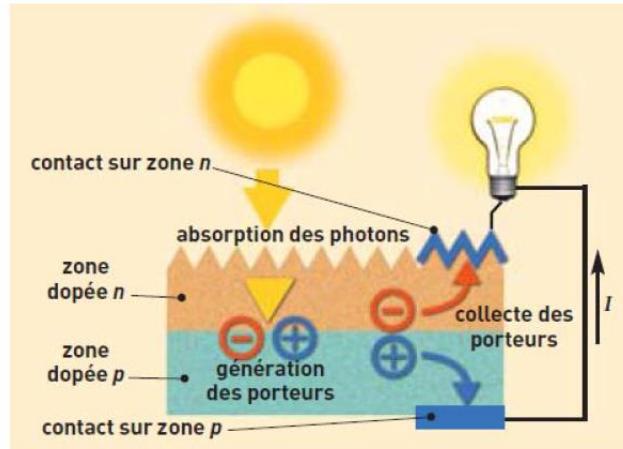

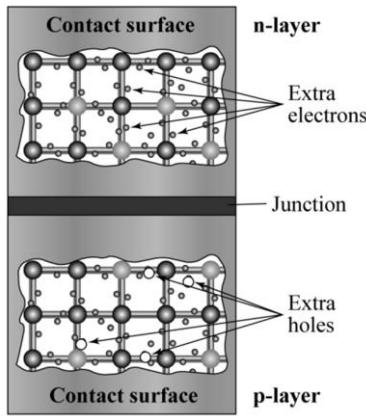

| I.2.3. Light Absorption                                                                                      | 8           |

| I.2.4. Electron-Hole Pairs                                                                                   | 9           |

| I.3. Photovoltaic Cells                                                                                      | 9           |

| I.3.1. The PV Cell Working Principle                                                                         | 10          |

| I.3.2. Type of PV Cell                                                                                       | 10          |

| I.3.3. Mathematical Modeling of PV Module                                                                    | 13          |

| I.3.3.1. Two-Diode Model                                                                                     | 13          |

| I.3.3.2. Single-Diode Model                                                                                  | 15          |

| I.3.4. Model including Ohmic Losses                                                                          | 17          |

| I.3.4.1. Current-Based Model                                                                                 | 17          |

| I.3.4.2. Voltage-Based Model                                                                                 | 17          |

| I.3.5. Calculation of Cell Current Under Standard Reference Conditions of Temperature Tref and Irradiance G0 | 18          |

| I.3.5.1. Calculation of Saturation Current at Tref =298K                                                     | 18          |

| I.3.5.2. Calculation of Series Resistance at Tref                                                            | 18          |

| I.3.6. Calculation of Cell Current at any Temperature T and Irradiance G                                     | 19          |

| I.3.6.1. Calculation of Short-Circuit Current at Any Temperature and Irradiance                              | 19          |

| I.3.6.2. Calculation of Saturation Current at Any Temperature                                                | 20          |

| I.3.7. Characteristics of a PV Cell                                                                          | 20          |

| I.3.7.1. Open-Circuit Voltage                                                                                | 21          |

| I.3.7.2. Short-Circuit Current                                                                               | 21          |

| I.3.7.3. Power-Voltage Characteristic                                                                        | 21          |

| I.3.7.4. Fill Factor of a PV Cell                                                                            | 22          |

| I.3.7.5. Efficiency                                                                                          | 22          |

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

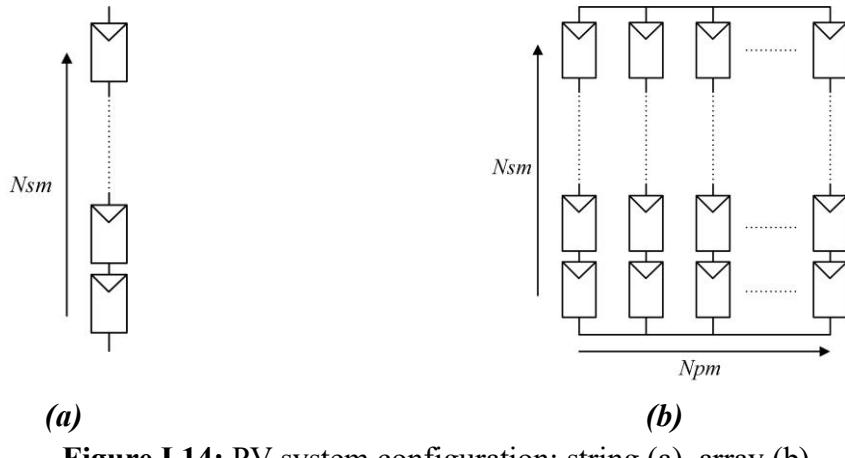

| I.3.8. Connection of Cells                                                               | 22 |

| I.3.8.1. Series Connection of Cells                                                      | 22 |

| I.3.8.2. Parallel Connection of Cells                                                    | 22 |

| I.3.8.3. Series-Parallel Connection of Cells (PV Array)                                  | 23 |

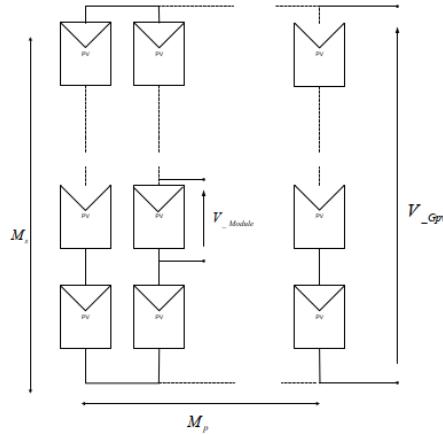

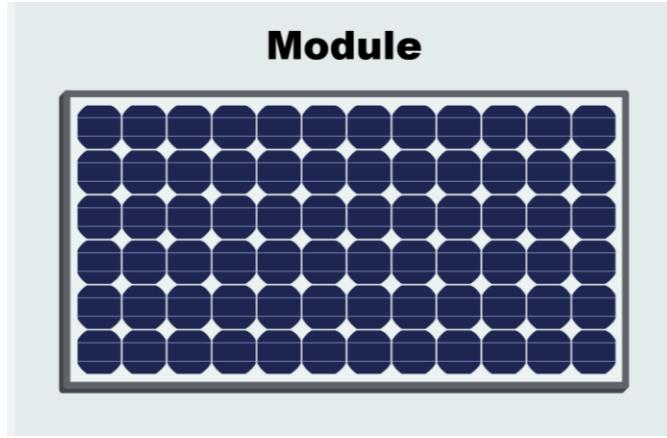

| I.4. Photovoltaic Module (Panel)                                                         | 23 |

| I.4.1. Modeling of Photovoltaic Module                                                   | 24 |

| I.4.1.1. Current Model                                                                   | 24 |

| I.4.1.2. Voltage Model                                                                   | 24 |

| I.5. Electrical Characteristics of a PV Module                                           | 25 |

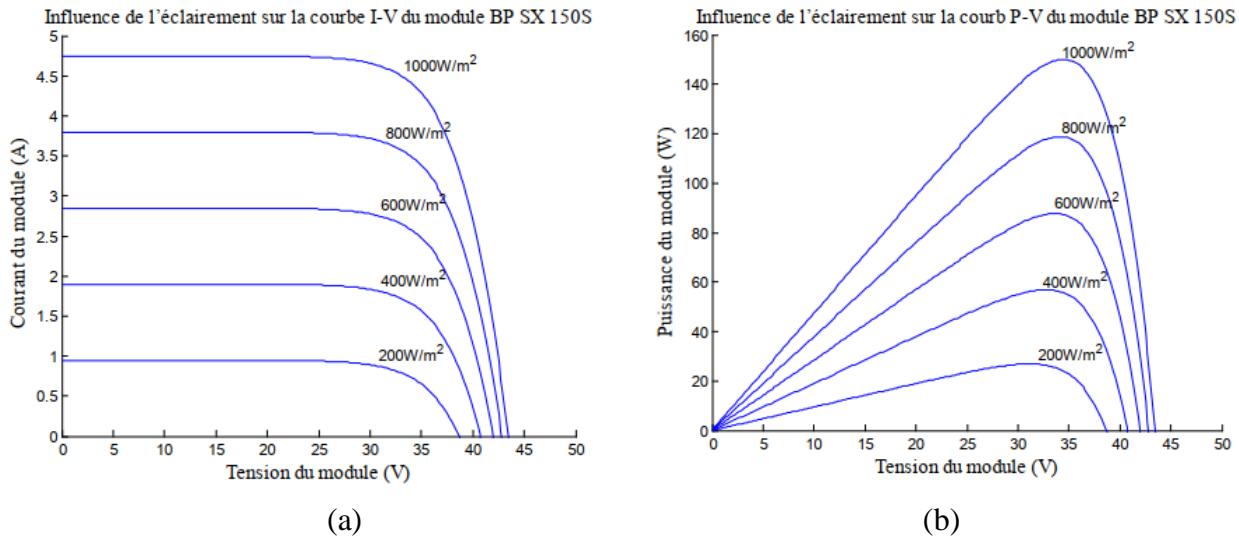

| I.5.1. Effect of Solar Irradiance on $I_{sc\_Module}$ , $V_{oc\_Module}$ , and $P_{max}$ | 26 |

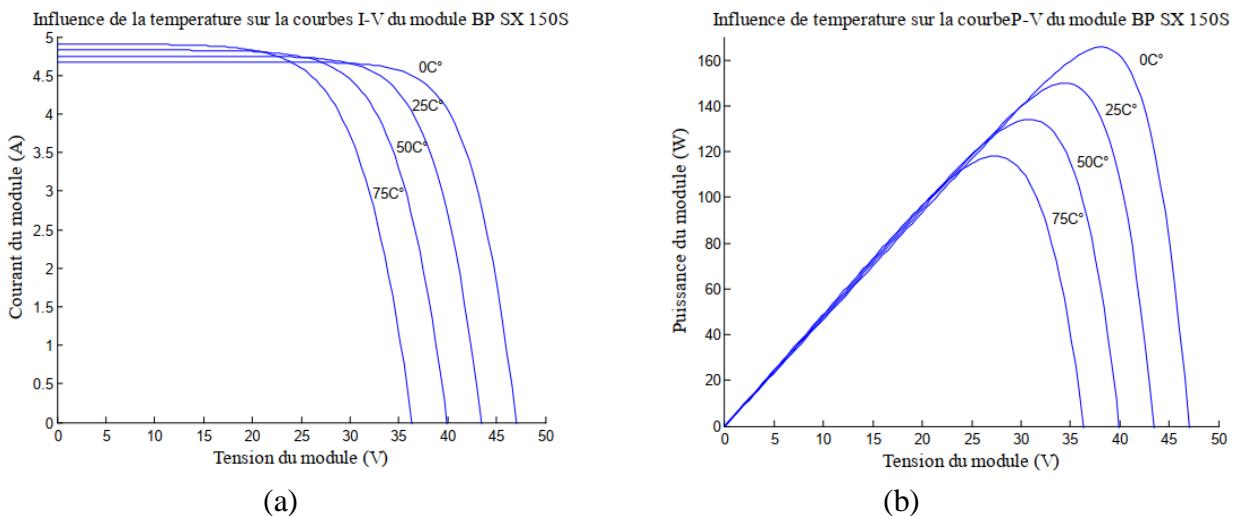

| I.5.2. Effect of Temperature on $I_{sc\_Module}$ , $V_{oc\_Module}$ , and $P_{max}$      | 27 |

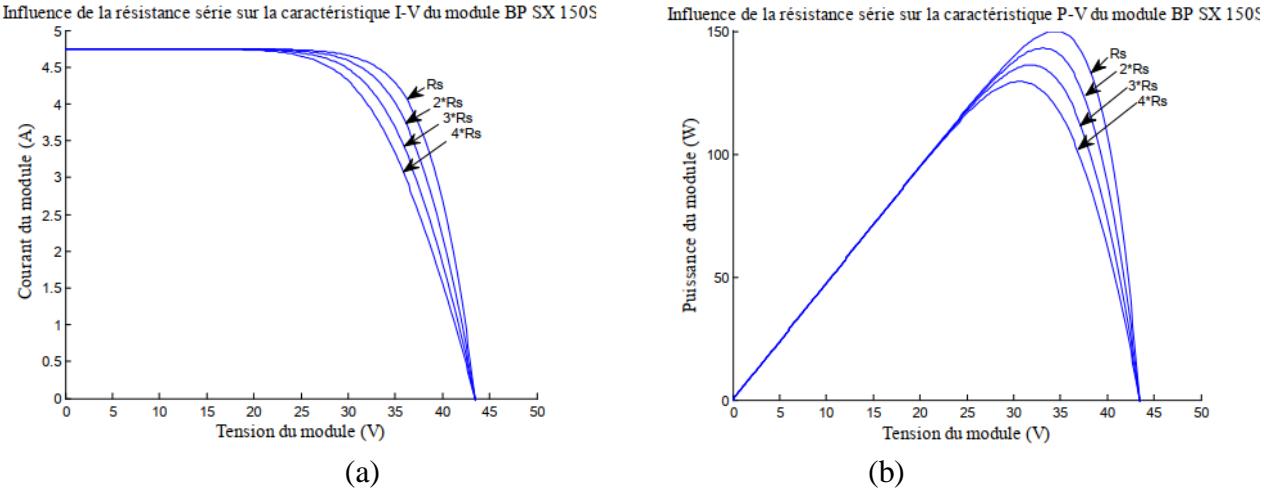

| I.5.3. Impact of Series Resistance                                                       | 27 |

| I.5.4. Partial shading influence on PV system's electrical characteristics               | 28 |

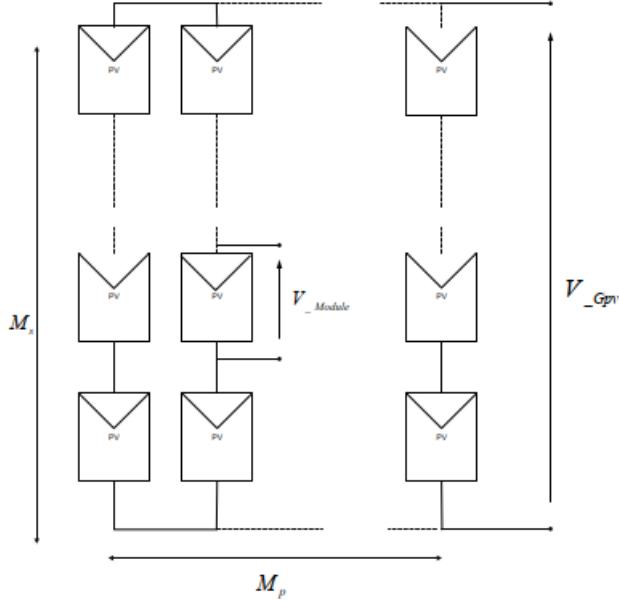

| I.6. Photovoltaic Generator structure and Modeling                                       | 28 |

| I.6.1. Structure of a PV Generator                                                       | 28 |

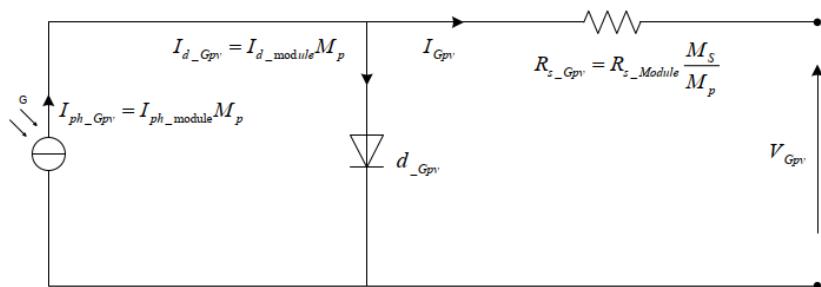

| I.6.2. Modeling of a PV Generator                                                        | 29 |

| I.6.2.1. PVG current model                                                               | 29 |

| I.6.2.2. PVG voltage model                                                               | 30 |

| I.7. PVG-based standalone power supply system                                            | 30 |

| I.7.1. DC-DC Converters                                                                  | 31 |

| I.7.2. Types of DC-DC Converters                                                         | 31 |

| I.7.2.1. Boost Converter                                                                 | 32 |

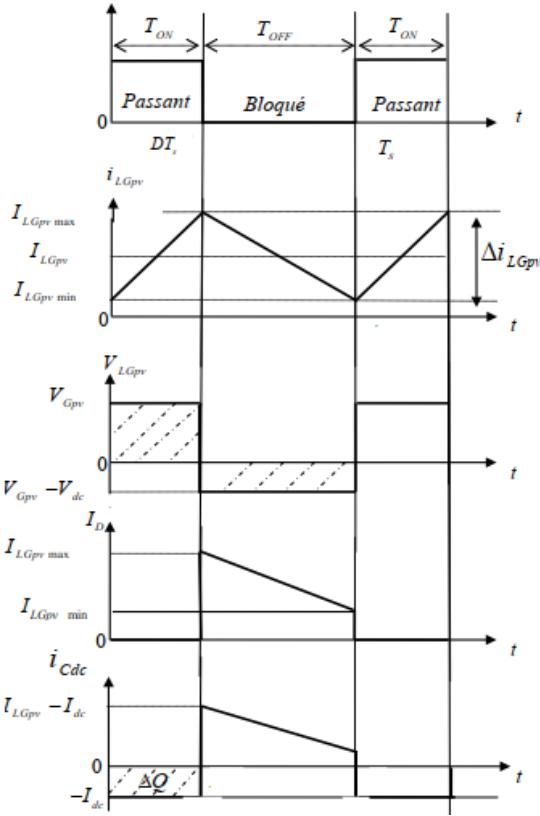

| I.7.2.2. Operating Principle of a boost converter                                        | 32 |

| I.7.2.3. Operation in Continuous Conduction Mode (CCM)                                   | 33 |

| I.7.2.3.1. Calculation of the input inductance value in CCM                              | 34 |

| I.7.2.3.2. Inductor current ripple                                                       | 36 |

| I.7.2.3.3. Output DC voltage ripple                                                      | 36 |

| I.7.2.4. Sizing of DC-DC boost converter components                                      | 37 |

| I.7.2.4.1. Sizing of DC-DC boost converter's input inductor                              | 37 |

| I.7.2.4.2. Sizing of DC-DC boost converter's output capacitor                            | 37 |

| I.7.2.4.3. Sizing of DC-DC boost converter's input capacitor                             | 38 |

| I.8. Pulse Width Modulation (PWM) Principle                                              | 38 |

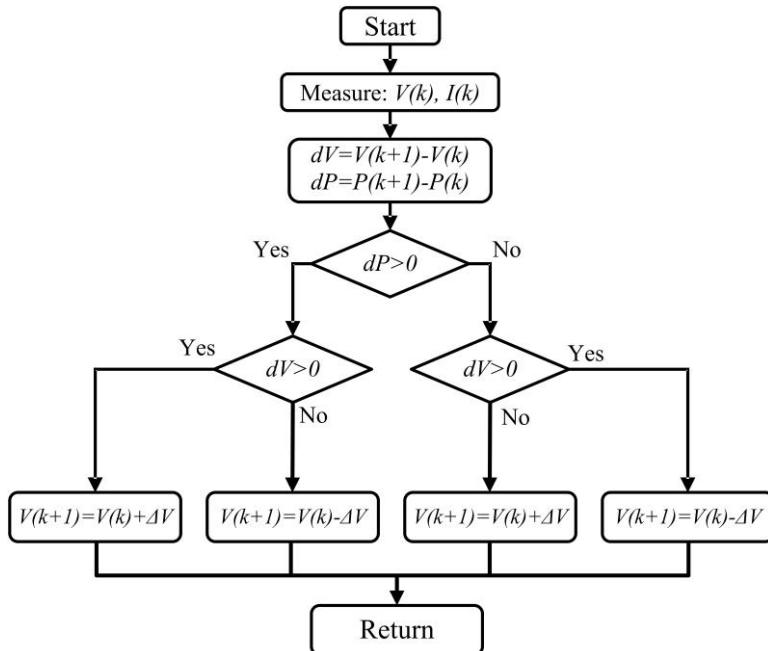

| I.9. Maximum Power Point Tracking Algorithms                                             | 38 |

| I.9.1. Perturb And Observe                                                               | 39 |

| I.9.2. Incremental Conductance                                                           | 40 |

| I.9.3. Sliding Mode MPPT Algorithm                                                       | 41 |

| I.9.4. Artificial Neural Network MPPT                                                    | 42 |

| I.9.5. Fuzzy Logic Controller                                                            | 42 |

| I.9.6. Meta-Heuristic and Bio-Inspired Techniques                                        | 43 |

| I.10. Linear Control of the Boost Converter                                              | 45 |

| I.10.1. Synthesis of the PI controller for the PVG output voltage                        | 46 |

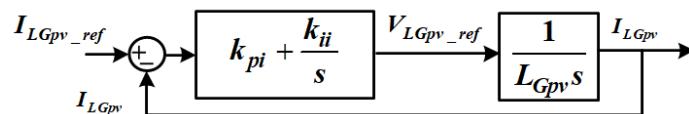

| I.10.2. Synthesis of the PI controller for input inductor current                        | 47 |

| I.11. Conclusion                                                                         | 48 |

## Chapter 2: Modeling and control of PVG four leg inverter in the grid connected system

|                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------|----|

| II.1. Introduction                                                                                             | 50 |

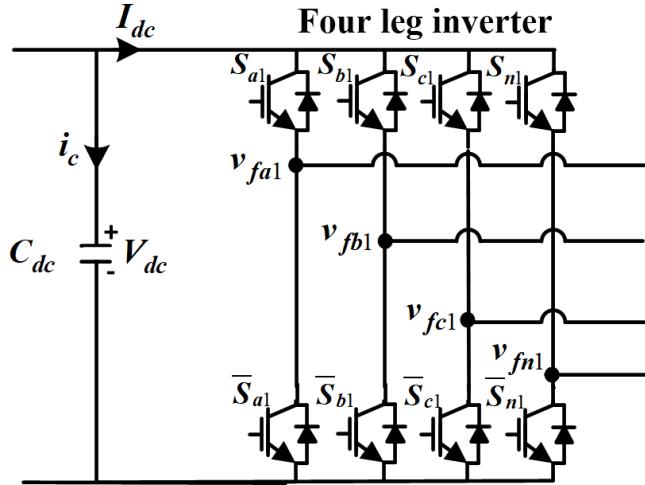

| II.2. Modeling and operating principle of the 4LI                                                              | 51 |

| II.2.1. Operating principle of the 4LI                                                                         | 51 |

| II.2.1.1. Output voltages of the 4LI                                                                           | 51 |

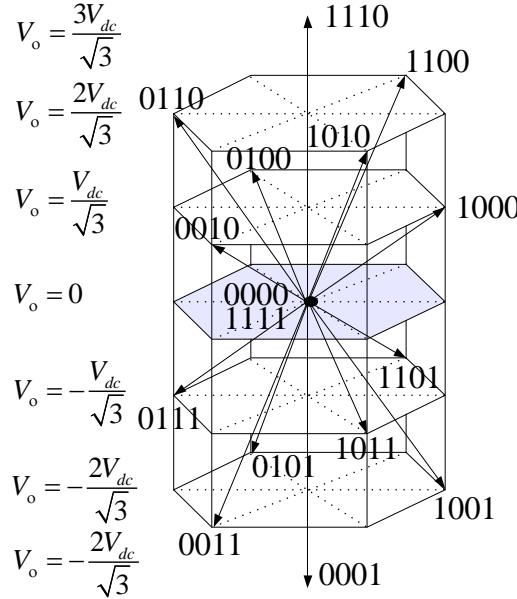

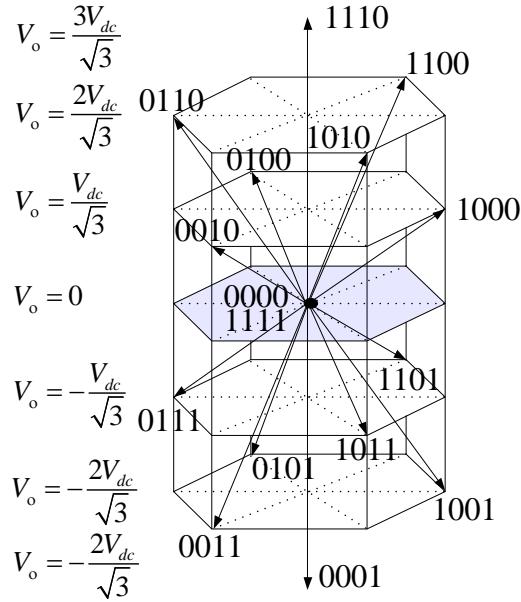

| II.2.1.2. Representation Vectorial of the 4LI                                                                  | 53 |

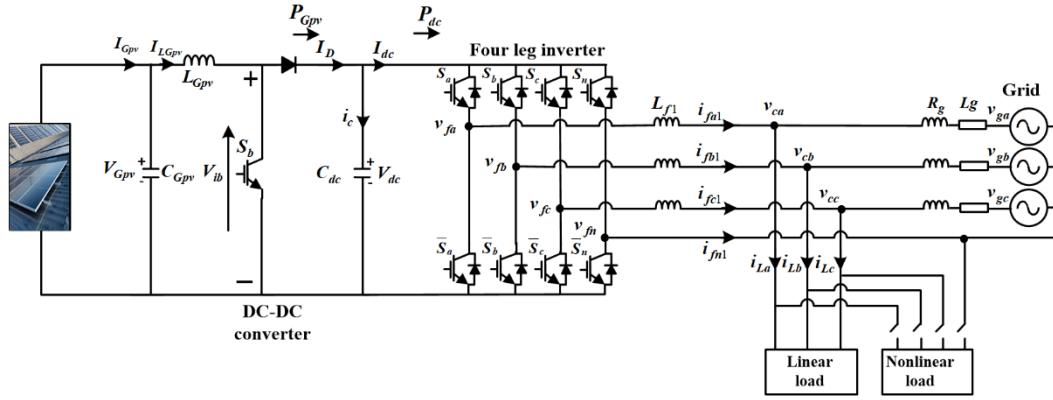

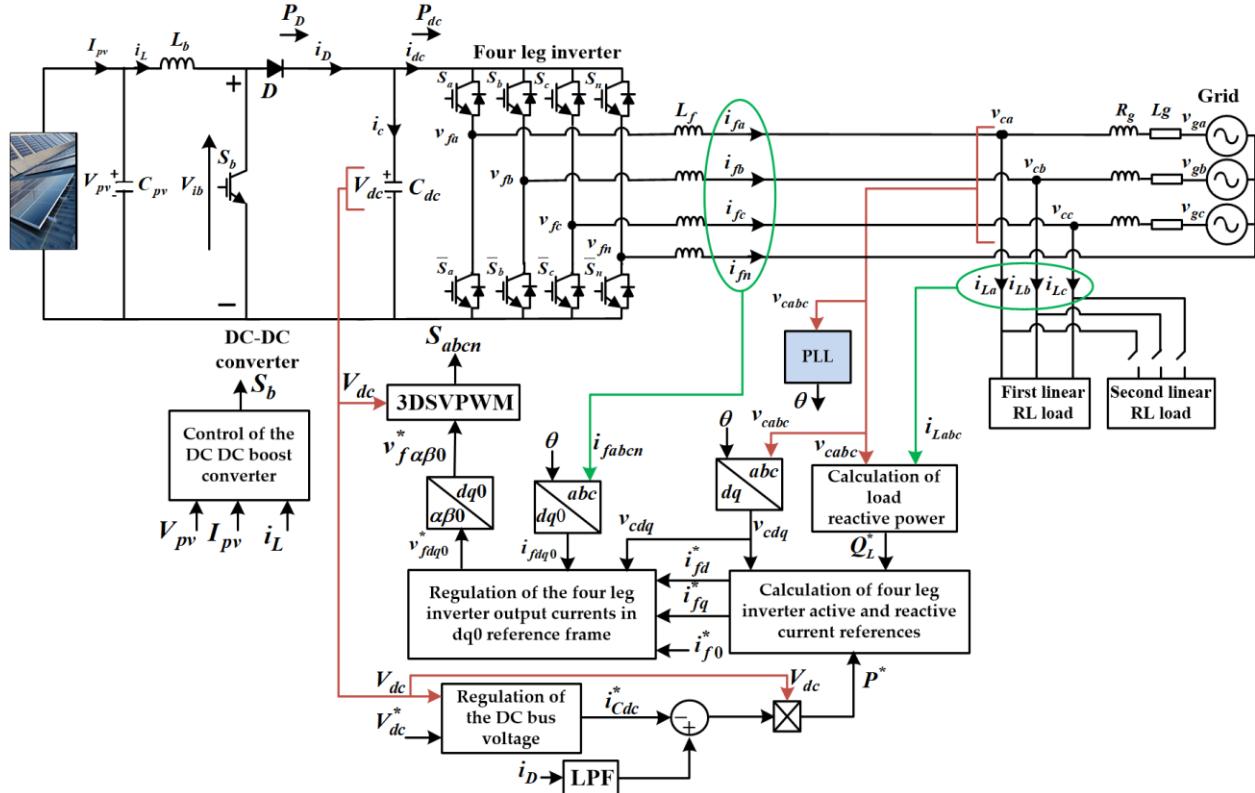

| II.3. Description and Modeling of a PVG Grid-Connected 4LI                                                     | 55 |

| II.3.1. Modelling of the PVG grid connected 4LI                                                                | 56 |

| II.3.1.1. Model of the PVG                                                                                     | 56 |

| II.3.1.2. Model of the grid connected 4LI                                                                      | 56 |

| II.3.1.2.1. Four leg inverter output current dynamics                                                          | 56 |

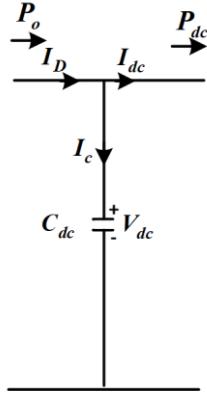

| II.3.1.2.2. DC bus voltage dynamic                                                                             | 58 |

| II.3.1.2.3. Relationship between AC and DC sides of the 4LI                                                    | 59 |

| II.3.1.3. Sizing of 4LI's input and output passive filters                                                     | 60 |

| II.3.1.3.1. Sizing of 4LI's input DC capacitor                                                                 | 60 |

| II.3.1.3.2. Sizing of 4LI's output filter inductor                                                             | 61 |

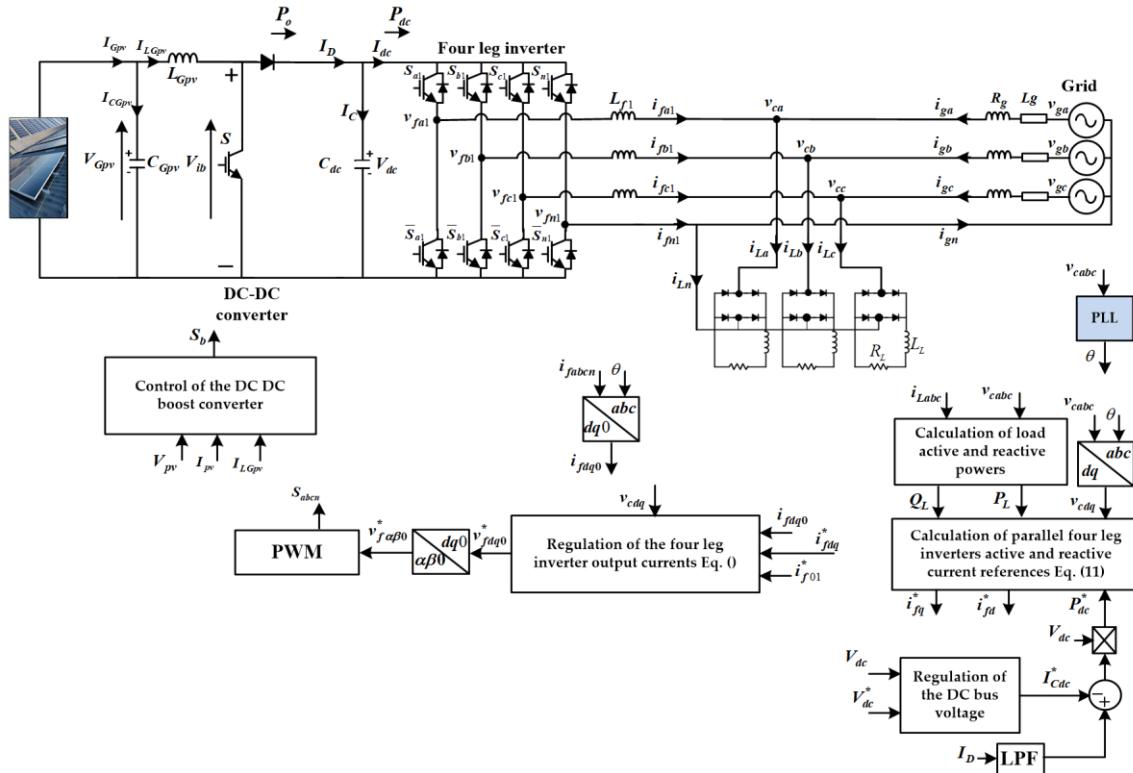

| II.4. Control of the 4LI-based PVG grid connected on mode harmonic filtrations and reactive power compensation | 62 |

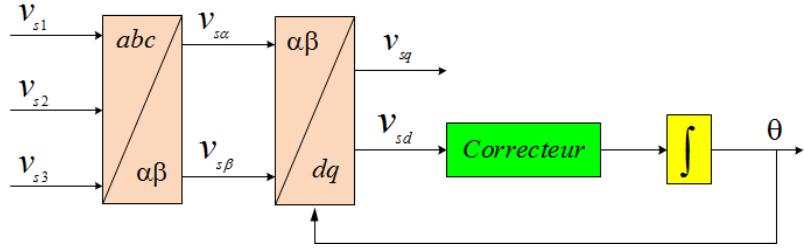

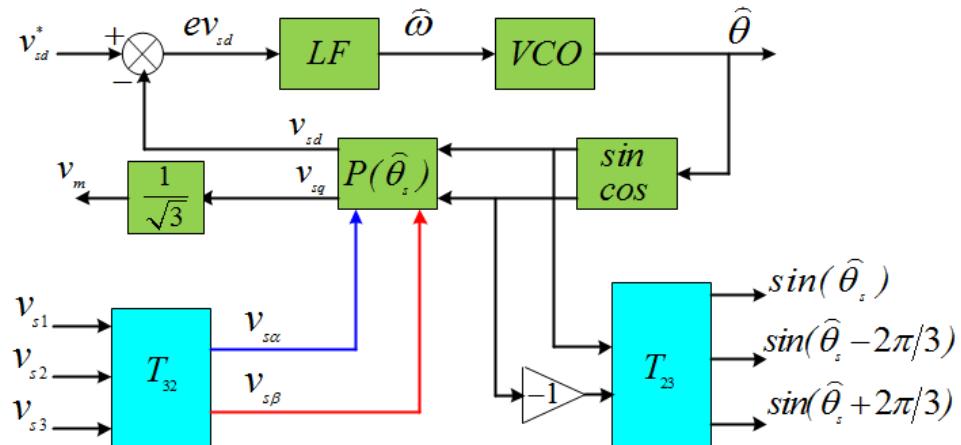

| II.4.1. Synchronization method                                                                                 | 64 |

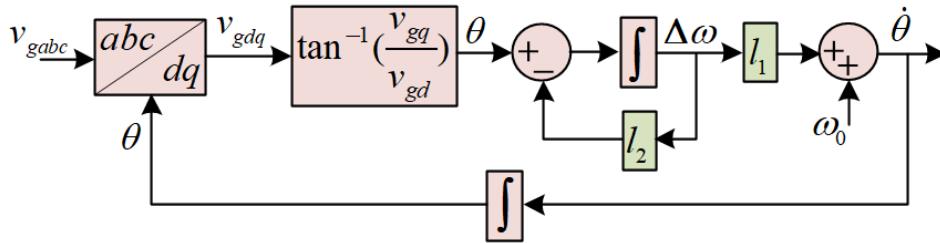

| II.4.1.1. Phase-Locked Loop (PLL)                                                                              | 64 |

| II.4.1.2. Robust synchronization PLL unit                                                                      | 66 |

| II.4.2. Detection of the 4LI's output current references                                                       | 67 |

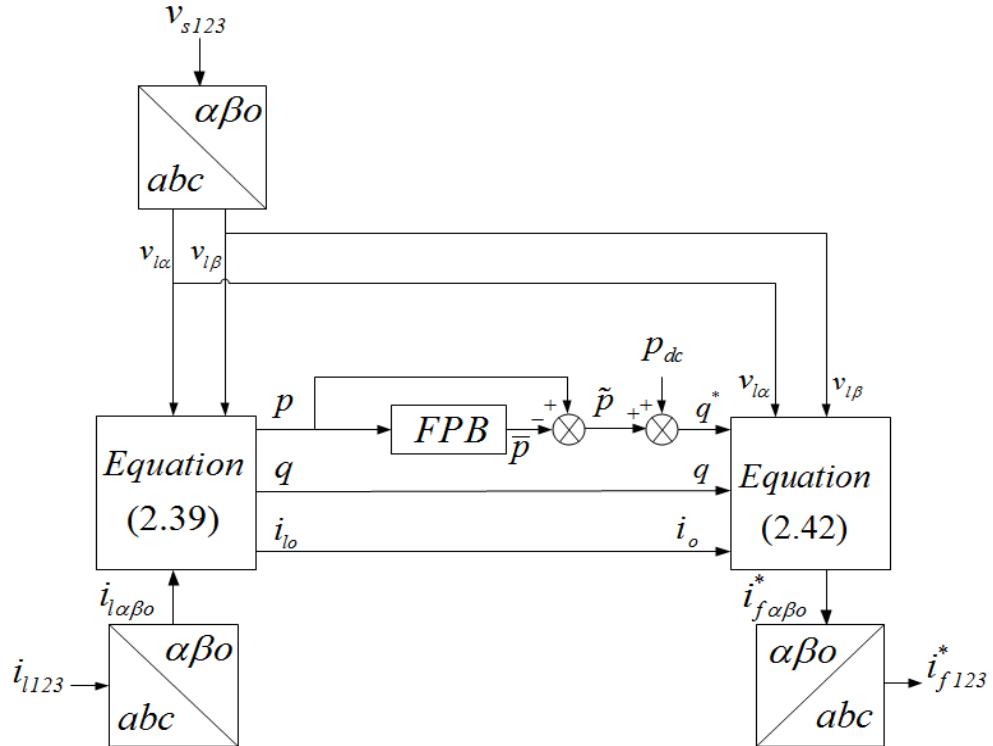

| II.4.2.1. Instantaneous power theory (pq0)                                                                     | 67 |

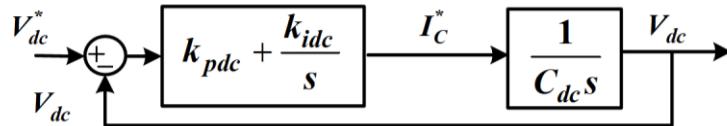

| II.4.3. Regulation of the 4LI's input DC voltage                                                               | 70 |

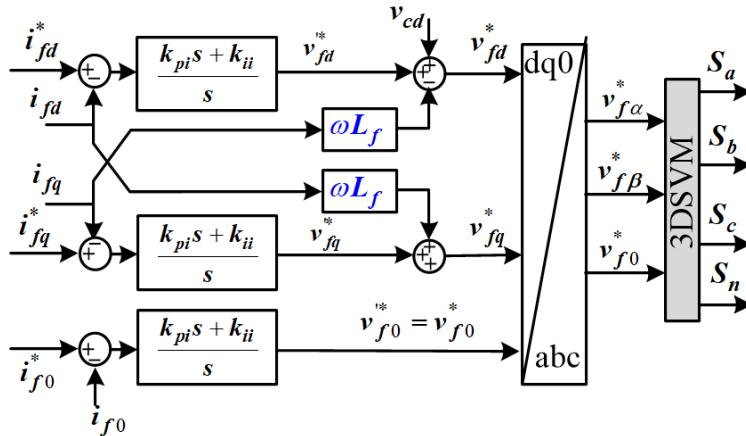

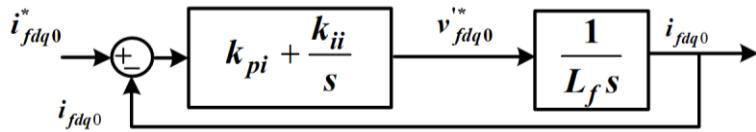

| II.4.4. Regulation of the 4LI output currents                                                                  | 71 |

| II.4.5. PWM generation techniques for 4LI                                                                      | 73 |

| II.4.5.1. Three-Dimensional Space Vector Modulation (3D SVM)                                                   | 73 |

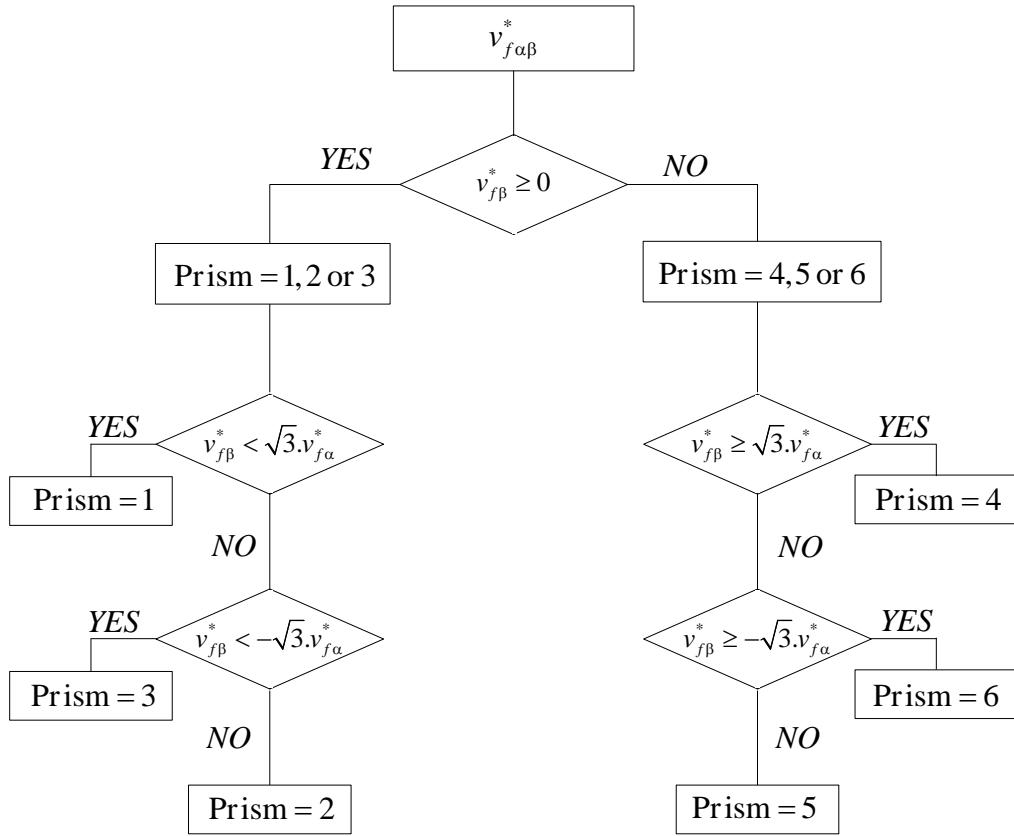

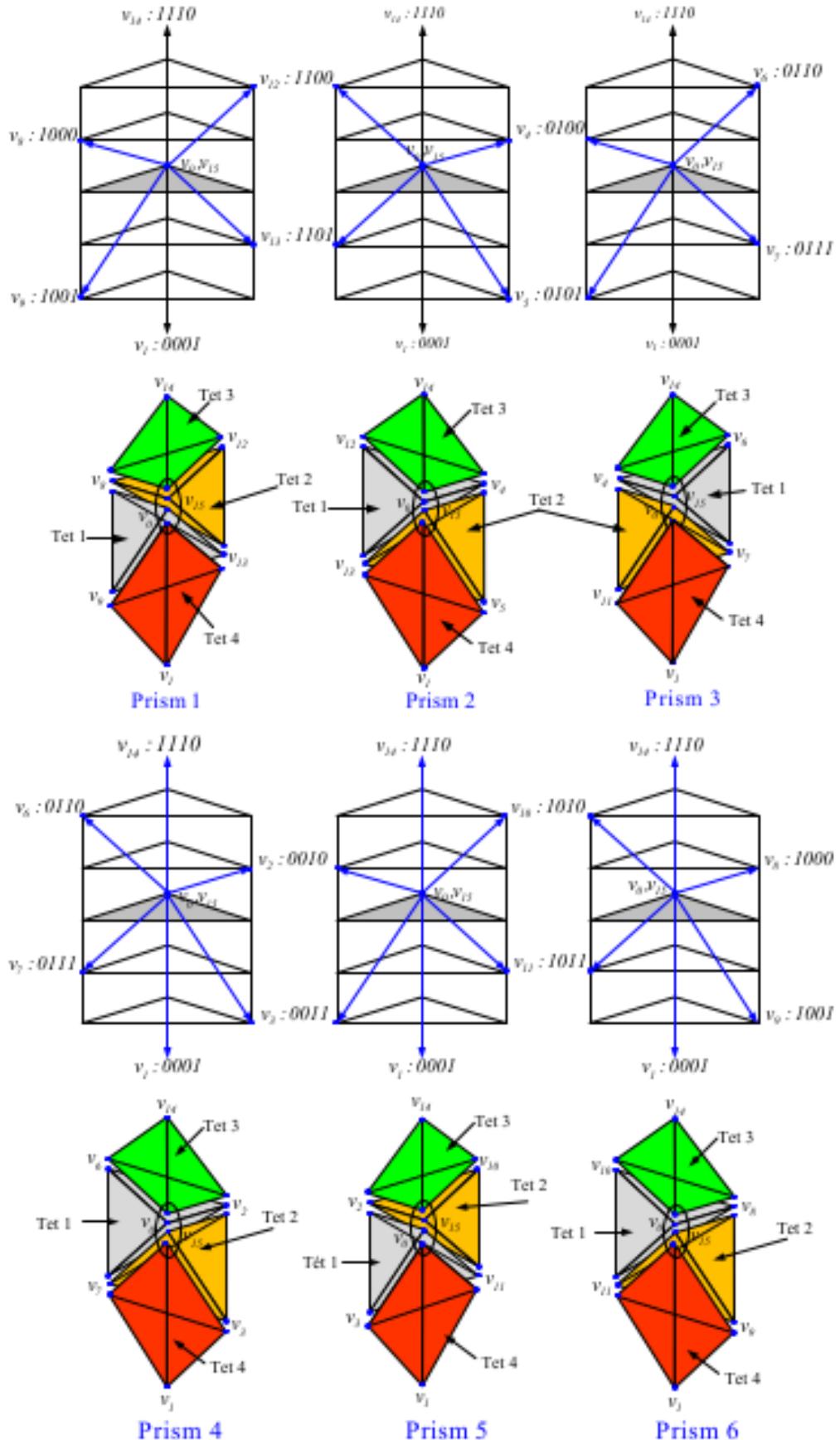

| II.4.5.1.1. Identification of the Prism and Reference Vectors                                                  | 74 |

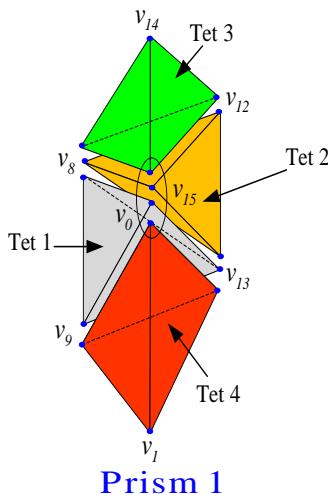

| II.4.5.1.2. Identification of Tetrahedrons                                                                     | 75 |

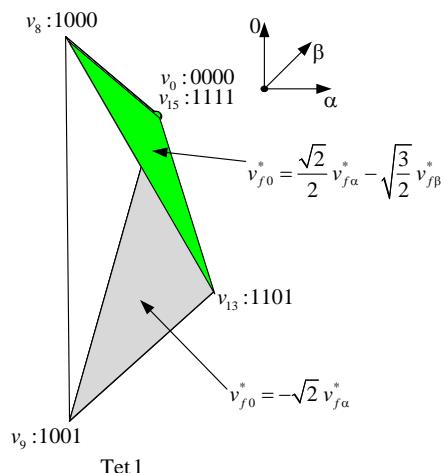

| II.4.5.1.3. Projection of the reference voltage vector                                                         | 79 |

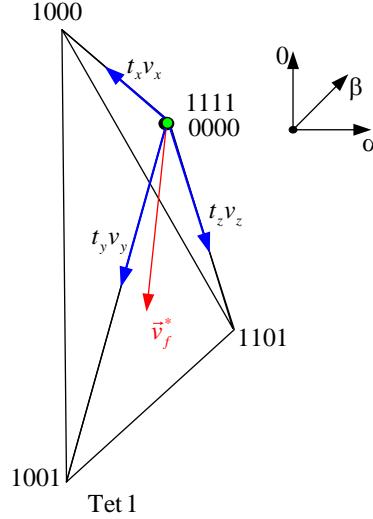

| II.4.5.1.4. Control pulses Generation                                                                          | 83 |

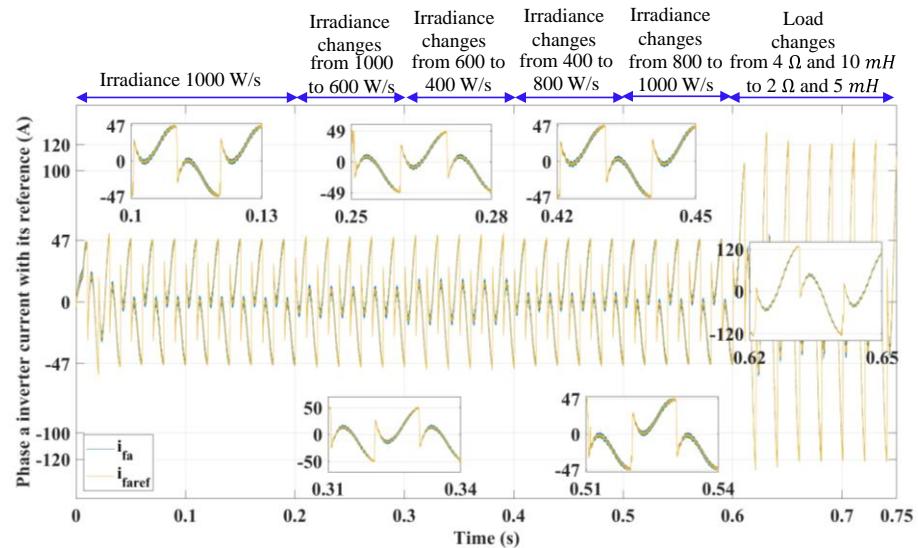

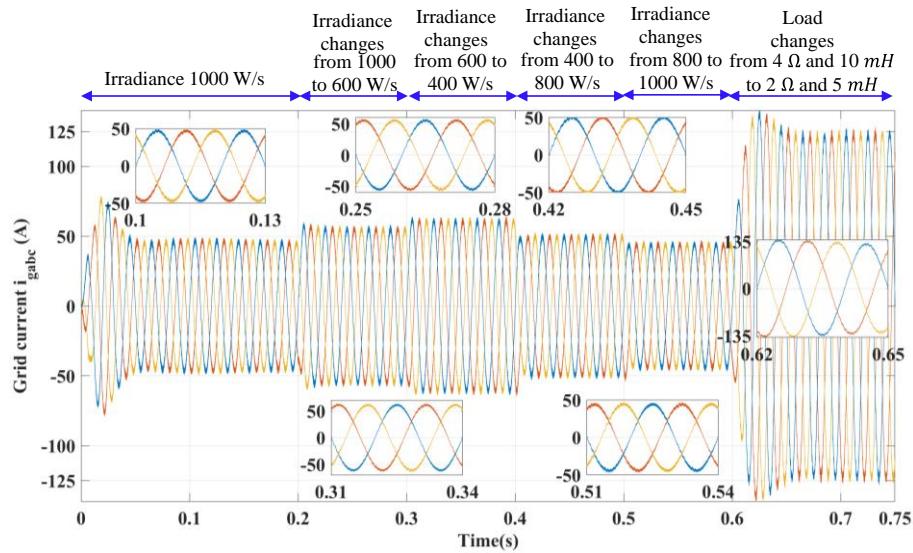

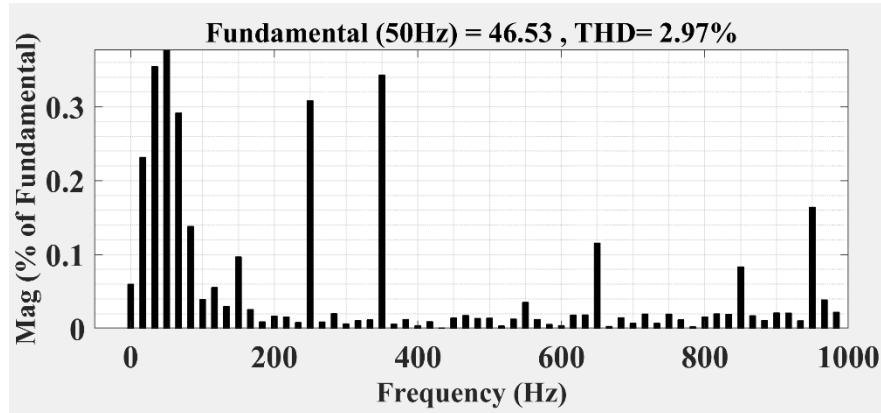

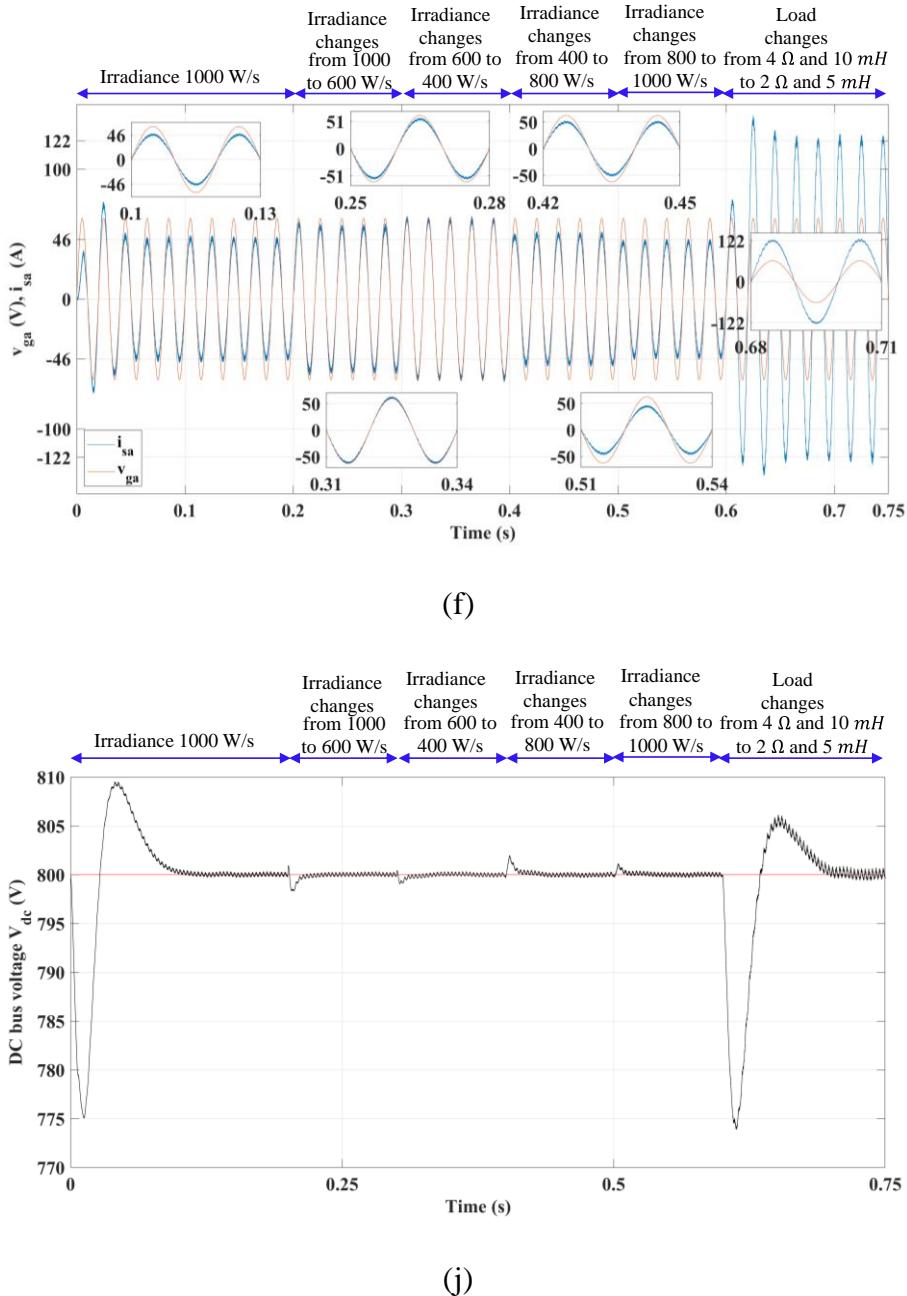

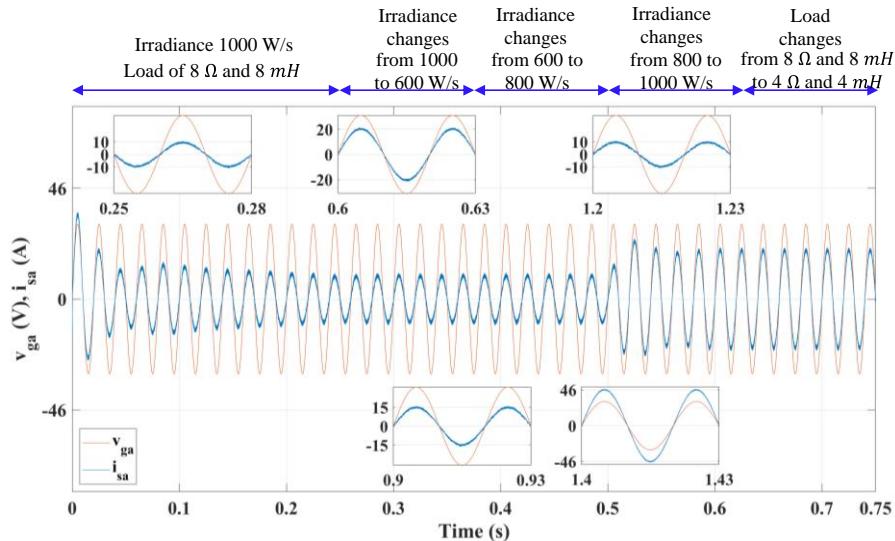

| II.4.6. Simulation results and discussion                                                                      | 83 |

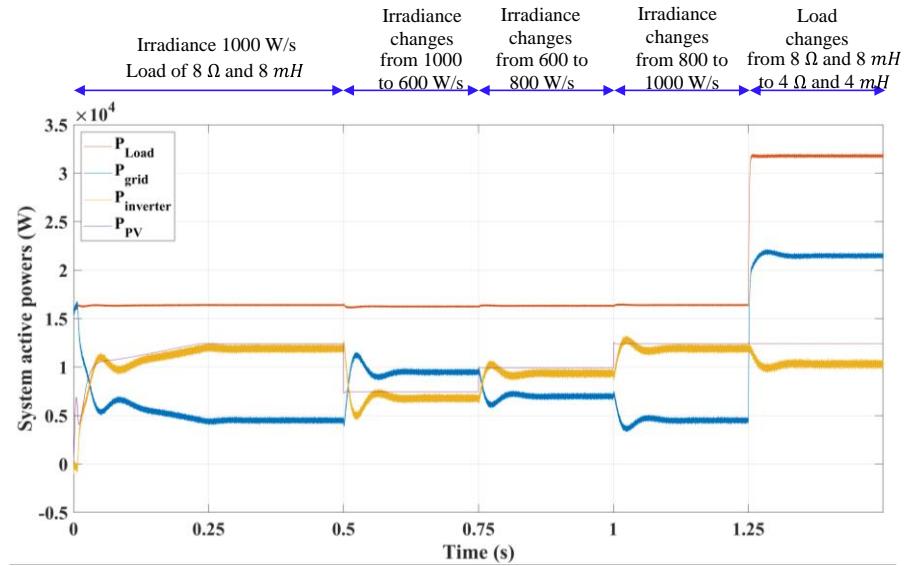

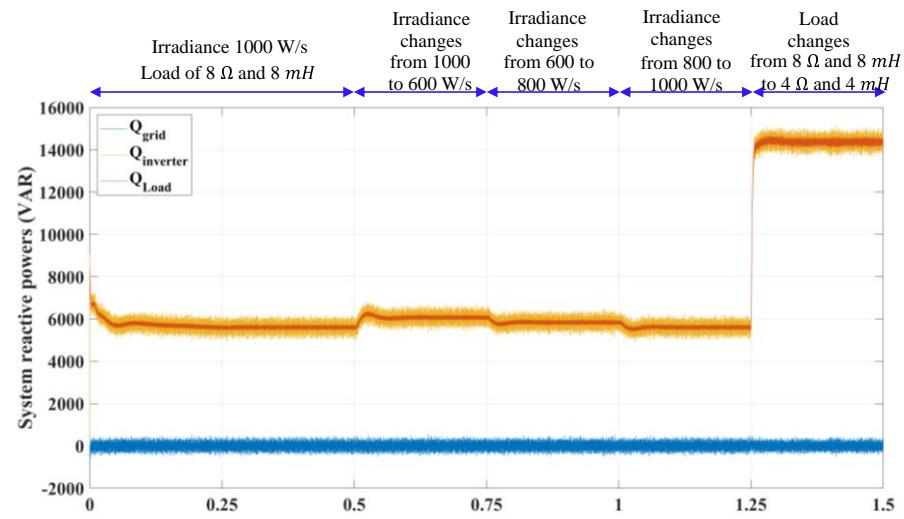

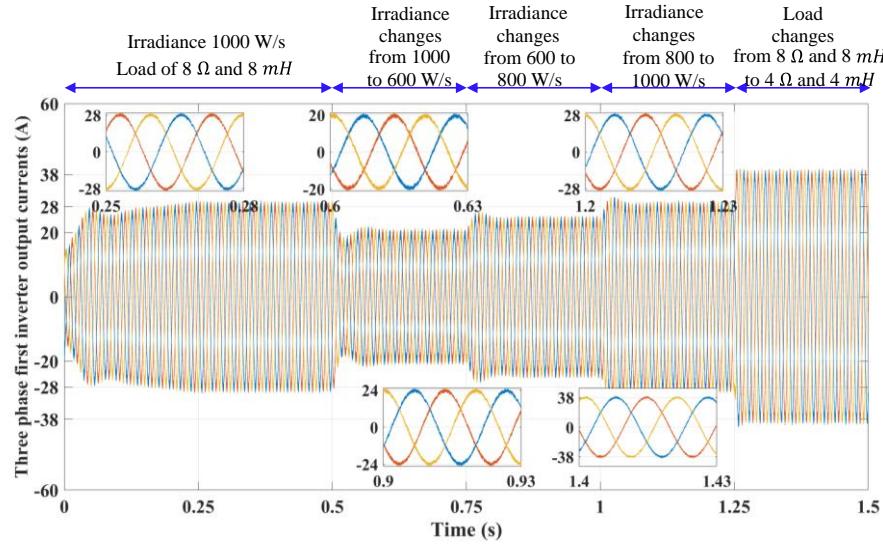

| II.4.6.1. System performance assessment under sudden solar irradiance and nonlinear load changes               | 83 |

| II.5. Control of the 4LI-based PVG grid connected for reactive power compensation mode under linear load       | 89 |

| II.5.1. Detection of the 4LI's output current references in mode reactive power compensation                   | 90 |

| II.5.2. Simulation Results and Discussion                                                                      | 91 |

| II.5. Conclusion                                                                                               | 96 |

### **Chapter 3: Modeling and linear control of PVG grid connected parallel four leg inverters system**

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| III.1. Introduction                                                               | 98  |

| III.2. State of the art on ZSCC elimination techniques in parallel 4LIs           | 99  |

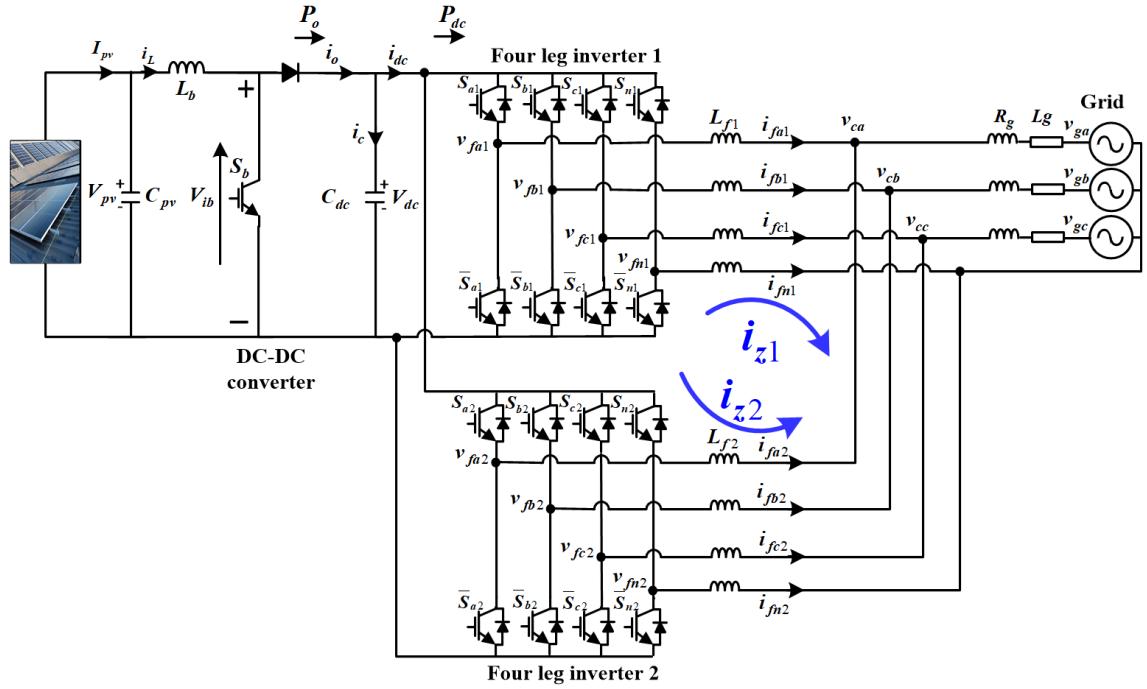

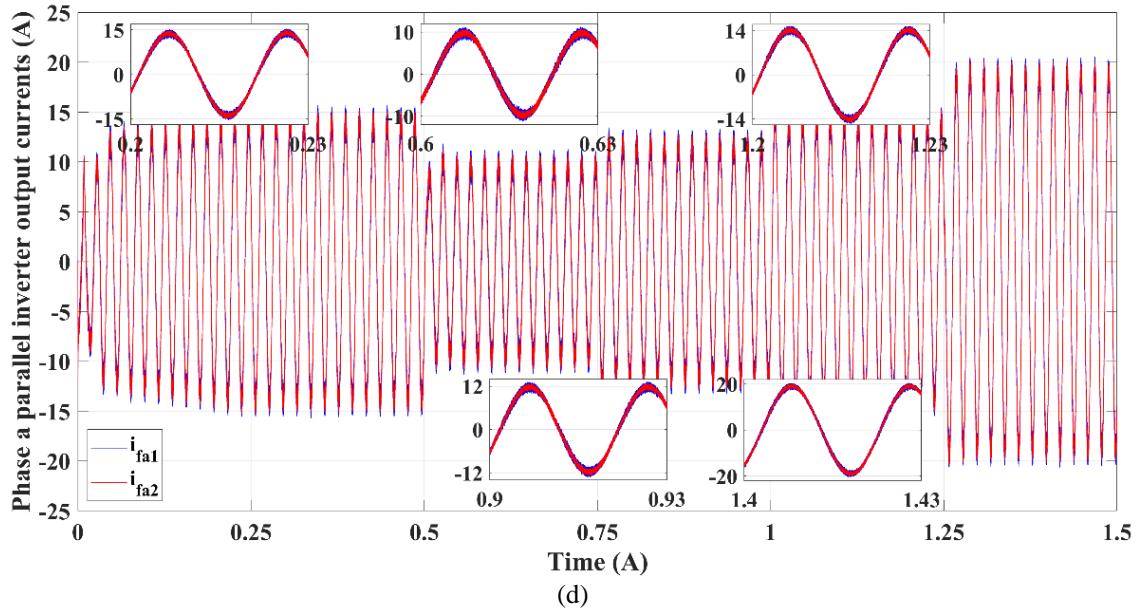

| III.3. Topology and modeling of the parallel 4LIs-based PVG grid connected system | 101 |

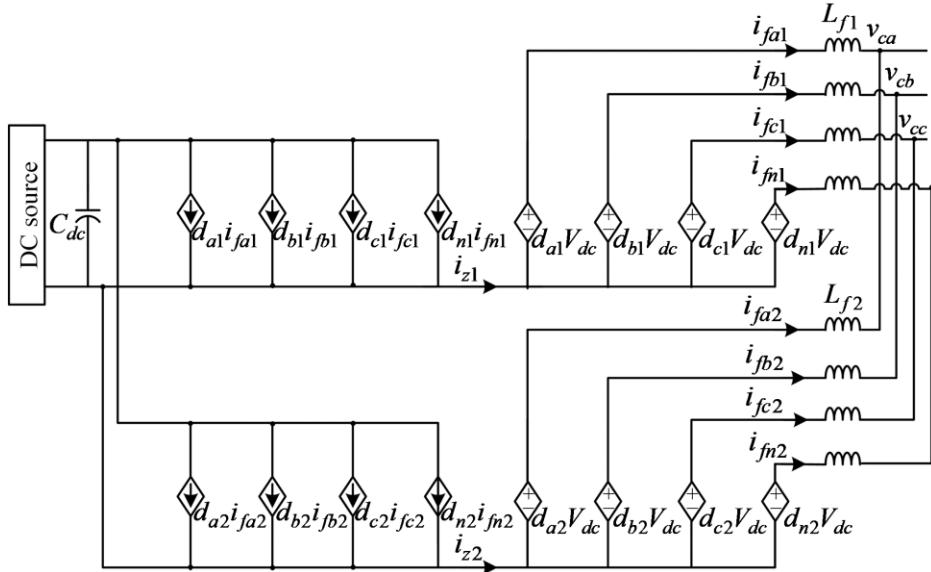

| III.3.1. Parallel system output current dynamics                                  | 102 |

|                                                                                                   |     |

|---------------------------------------------------------------------------------------------------|-----|

| III.3.2. Parallel system DC bus voltage dynamic                                                   | 105 |

| III.3.3. ZSCC characteristics and modeling                                                        | 105 |

| III.4. ZSCC control and elimination in parallel 4LIs-based PV grid connected system               | 108 |

| III.4.1. Adjusted SPWM modulation voltages approach                                               | 108 |

| III.4.1.1. ZSCC regulation-based adjusted SPWM modulation voltages approach                       | 110 |

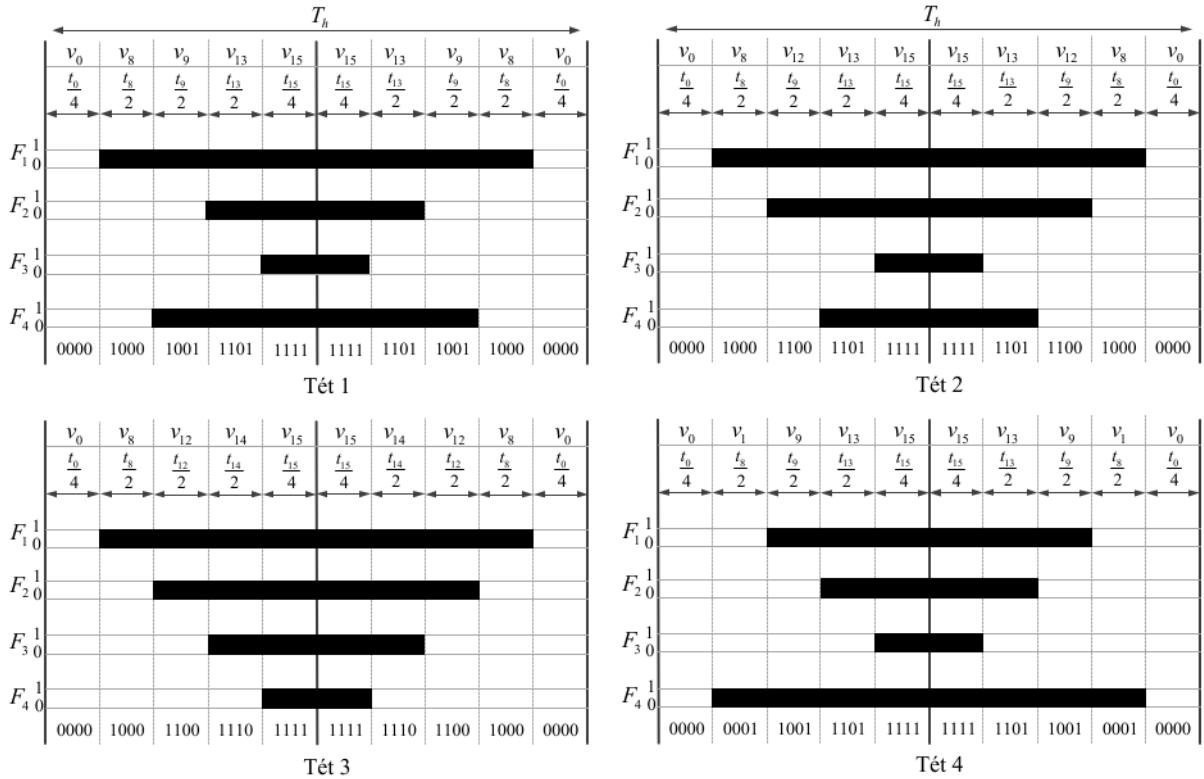

| III.4.2. Adjusted 3DSVPWM's zero-vector duty ratios approach                                      | 110 |

| III.4.2.1. ZSCC Regulation-based adjusted 3D-SVPWM approach                                       | 115 |

| III.5. Control of the parallel connected 4LIs-based reactive power compensation                   | 115 |

| III.5.1. Application of the adjusted modulation voltage references based SPWM                     | 115 |

| III.5.1.1. Regulation of the parallel system output currents                                      | 116 |

| III.5.1.2. Parallel 4LI's system output current references                                        | 117 |

| III.5.1.3. Active power reference                                                                 | 117 |

| III.5.1.4. Simulation results and discussion                                                      | 117 |

| III.5.1.4.1. Performance of the parallel system under difference in the output filter inductances | 117 |

| III.6. Conclusion                                                                                 | 133 |

#### **Chapter 4: Active Disturbance Rejection Control method for PVG grid connected parallel four leg inverters system**

|                                                                                                 |     |

|-------------------------------------------------------------------------------------------------|-----|

| IV.1. Introduction                                                                              | 136 |

| IV.2. Uncertainty dynamics of the parallel 4LIs-based PVG grid connected system                 | 140 |

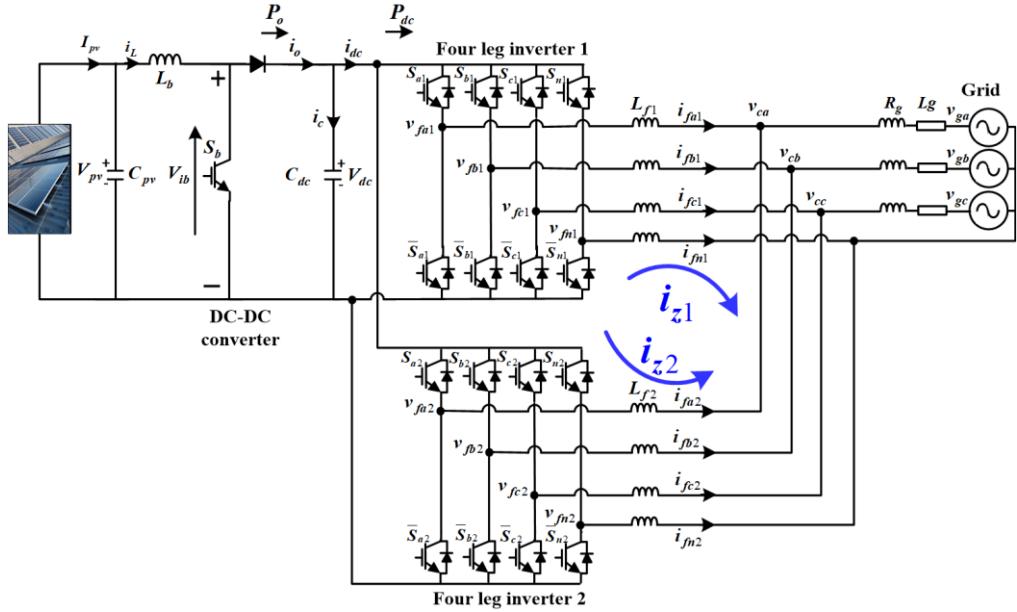

| IV.2.1. Uncertainty dynamic of the DC bus voltage                                               | 141 |

| IV.2.2. Uncertainty dynamics of parallel 4LIs output currents in the dq0 reference frame        | 142 |

| IV.4. Design of the ADRC method-based grid connected parallel 4LIs                              | 144 |

| IV.4.1. Design of the ADRC method-based outer DC bus voltage control loop                       | 144 |

| IV.4.1.1. Design of the ESO-based outer DC bus voltage control loop                             | 145 |

| IV.4.1.2. Design of the SEFC-based outer DC bus voltage control loop                            | 146 |

| IV.4.2. Design of the ADRC method-based inner output current control loop                       | 146 |

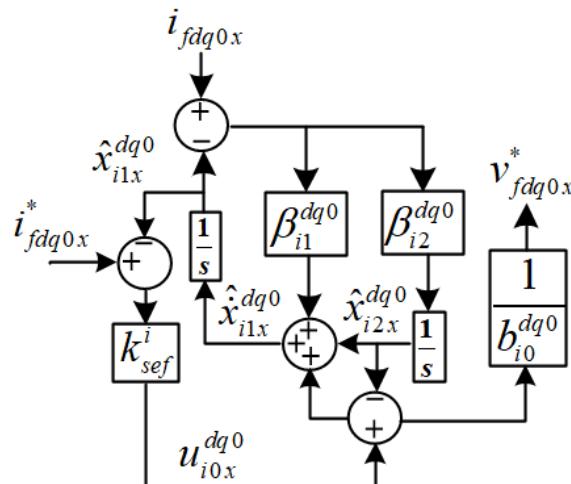

| IV.4.2.1. Design of the ESOs-based inner output current control loop in the dq0 reference frame | 147 |

| IV.4.2.2. Design of the SEFC-based inner output current control loop                            | 148 |

| IV.4.3. Parameter tuning and performance analysis of the proposed ADRC method                   | 148 |

| IV.5. ADRC method for PV grid connected parallel 4LIs-based reactive power compensation         | 150 |

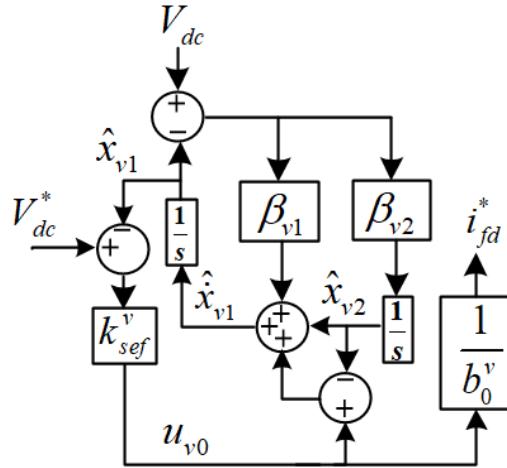

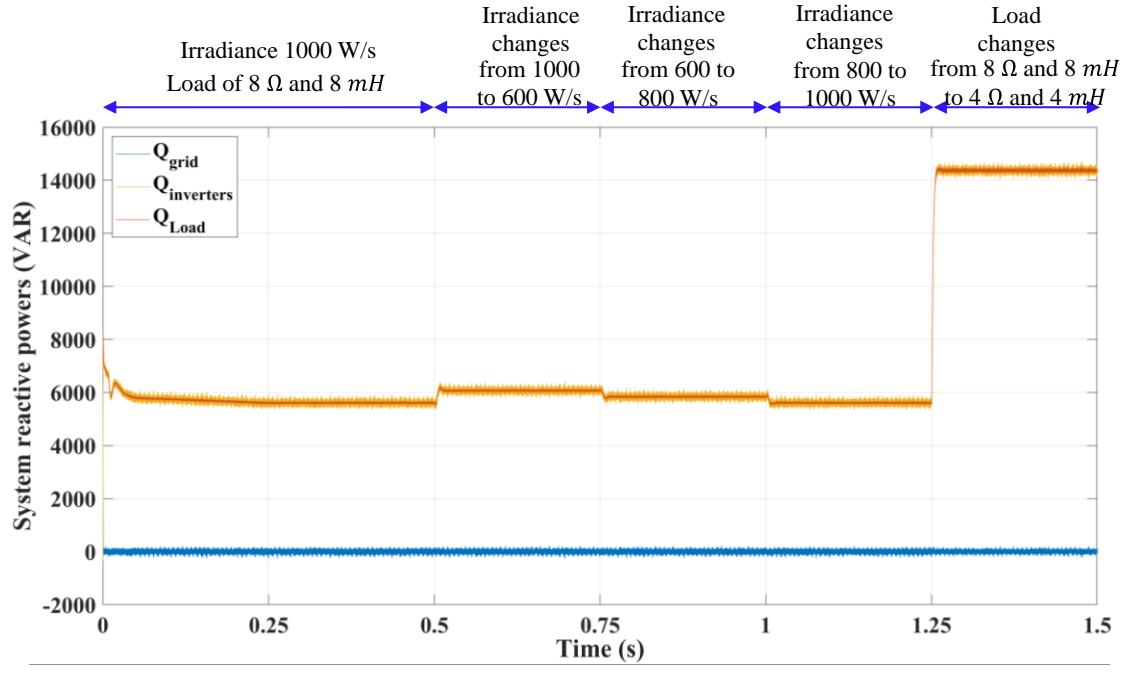

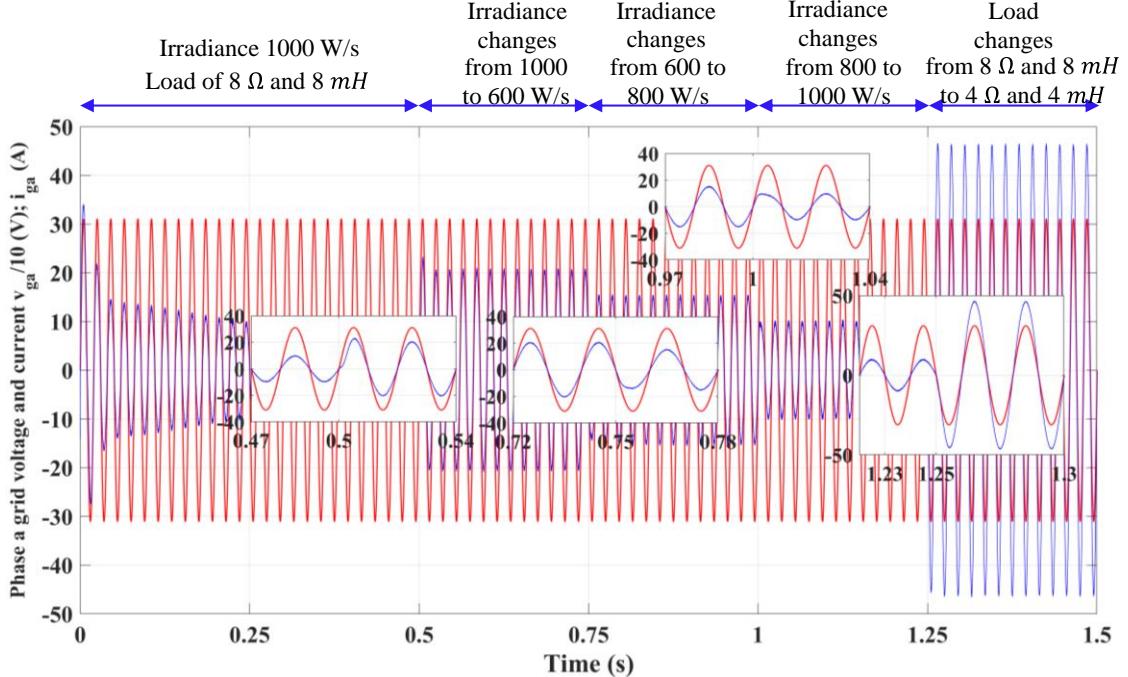

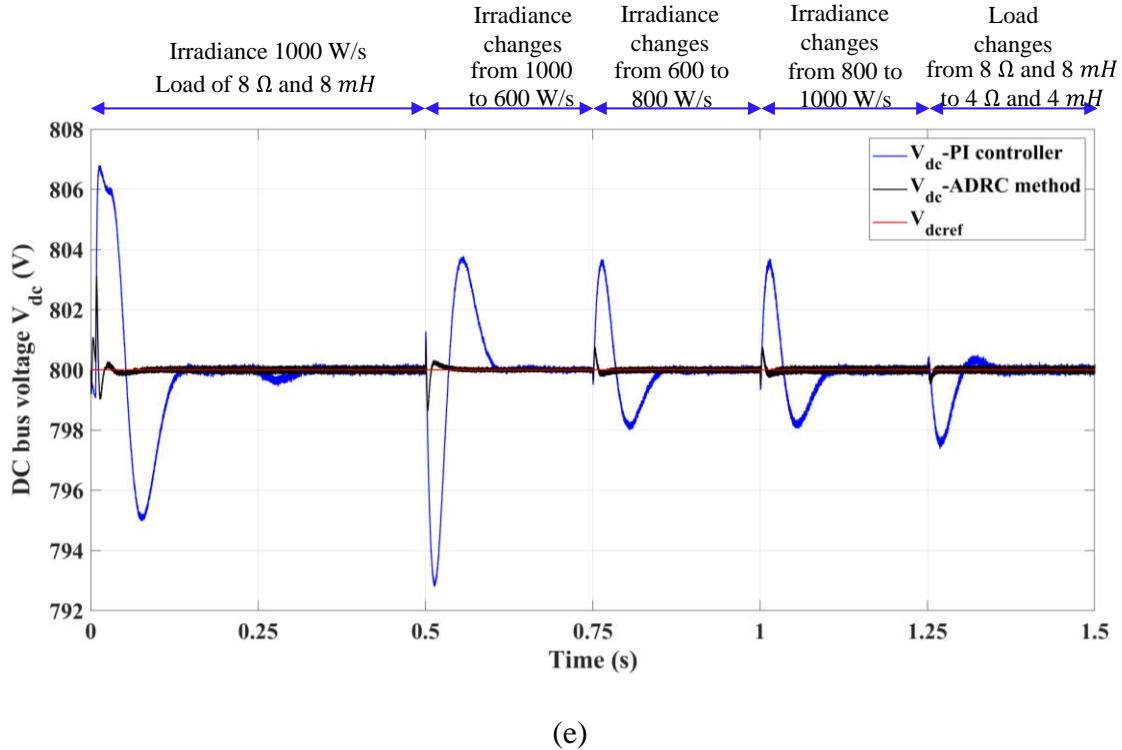

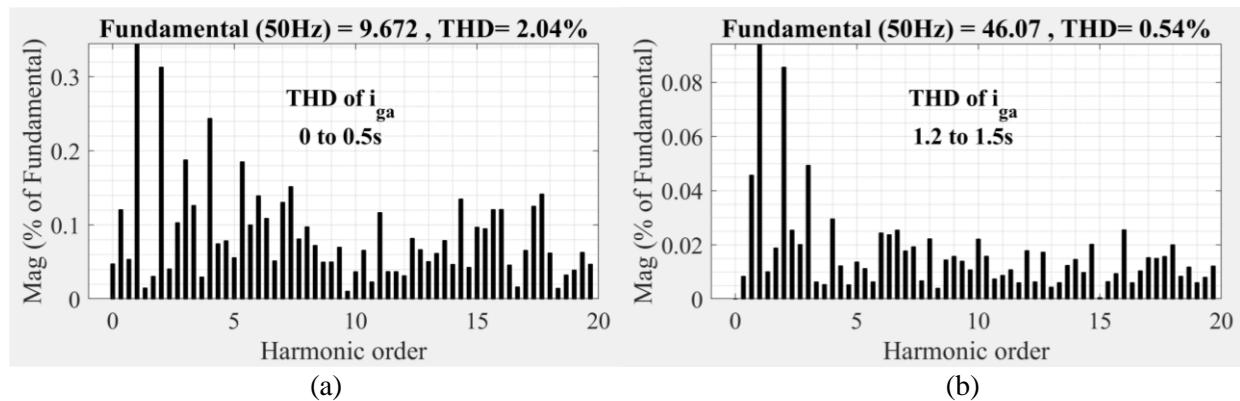

| IV.5.1. Key superiority aspects of ADRC method-based PV grid connected parallel 4LIs system     | 162 |

| IV.5.1.1. Disturbance rejection capability                                                      | 162 |

| IV.5.1.2. Robustness to output filters inductance parameter mismatches                          | 162 |

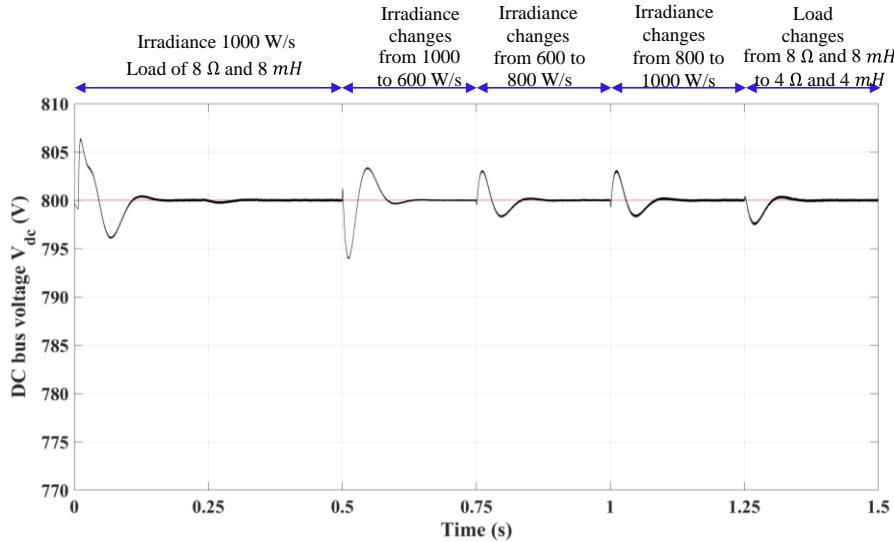

| IV.5.1.3. DC bus voltage regulation quality                                                     | 163 |

| IV.5.1.4. Grid current quality and THD                                                          | 163 |

| IV.5.1.5. Reactive power compensation precision                                                 | 163 |

| IV.5.1.6. Dynamic response during severe transients                                             | 163 |

| IV.5.1.7. Synergistic effect with adjusted 3D-SVPWM                                             | 164 |

| IV.6. Conclusion                                                                                | 166 |

## LIST OF ABBREVIATIONS

| <b>Abbreviation</b> | <b>Full Form</b>                                          |

|---------------------|-----------------------------------------------------------|

| ABC                 | Artificial Bee Colony                                     |

| AC                  | Alternating Current                                       |

| ACO                 | Ant Colony Optimization                                   |

| ADRC                | Active Disturbance Rejection Control                      |

| ANN                 | Artificial Neural Network                                 |

| APF                 | Active Power Filter                                       |

| AV                  | Active Vector                                             |

| CCM                 | Continuous Conduction Mode                                |

| CIGS                | Copper Indium Gallium Selenide                            |

| CS                  | Cuckoo Search                                             |

| DC                  | Direct Current                                            |

| DDBC                | DC-DC Boost Converter                                     |

| DDSRF-PLL           | Decoupled Double Synchronous Reference Frame PLL          |

| DG                  | Distributed Generation                                    |

| DQ0                 | Direct-Quadrature-Zero (reference frame)                  |

| DSP                 | Digital Signal Processor                                  |

| EMI                 | Electromagnetic Interference                              |

| ESO                 | Extended State Observer                                   |

| ESR                 | Equivalent Series Resistance                              |

| FFT                 | Fast Fourier Transform                                    |

| FL                  | Fuzzy Logic                                               |

| FOSM                | First-Order Sliding Mode                                  |

| FPGA                | Field-Programmable Gate Array                             |

| GA                  | Genetic Algorithm                                         |

| GaAs                | Gallium Arsenide                                          |

| GMPP                | Global Maximum Power Point                                |

| GWO                 | Grey Wolf Optimizer                                       |

| HOSM                | High-Order Sliding Mode                                   |

| IC                  | Incremental Conductance                                   |

| ICPSO               | Incremental Conductance based Particle Swarm Optimization |

| IEEE                | Institute of Electrical and Electronics Engineers         |

| IGBT                | Insulated Gate Bipolar Transistor                         |

| LADRC               | Linear Active Disturbance Rejection Control               |

| LC                  | Inductor-Capacitor (filter)                               |

| LFHC                | Low-Frequency Harmonic Component                          |

| LPF                 | Low-Pass Filter                                           |

| LTD                 | Lumped Total Disturbance                                  |

| <b>Abbreviation</b> | <b>Full Form</b>                                  |

|---------------------|---------------------------------------------------|

| MIMO                | Multi-Input Multi-Output                          |

| MPC                 | Model Predictive Control                          |

| MPP                 | Maximum Power Point                               |

| MPPT                | Maximum Power Point Tracking                      |

| MOSFET              | Metal-Oxide-Semiconductor Field-Effect Transistor |

| NREL                | National Renewable Energy Laboratory              |

| P&O                 | Perturb and Observe                               |

| PCC                 | Point of Common Coupling                          |

| PCE                 | Power Conversion Efficiency                       |

| PD                  | Phase Detector                                    |

| PI                  | Proportional-Integral (controller)                |

| PIQRC               | PI-Quasi-Resonant Controller                      |

| PLL                 | Phase-Locked Loop                                 |

| PN                  | P-type N-type (junction)                          |

| PSO                 | Particle Swarm Optimization                       |

| PV                  | Photovoltaic                                      |

| PVG                 | Photovoltaic Generator                            |

| PWM                 | Pulse Width Modulation                            |

| RER                 | Renewable Energy Resource                         |

| RPLL                | Robust PLL                                        |

| RSPLLU              | Robust Synchronization PLL Unit                   |

| SAPF                | Shunt Active Power Filter                         |

| SAPSS               | Standalone Active Power Supply System             |

| SD                  | Single-Diode (model)                              |

| SEFC                | State Error Feedback Controller                   |

| SMC                 | Sliding Mode Control                              |

| SOGI-PLL            | Second-Order Generalized Integrator PLL           |

| SPWM                | Sinusoidal Pulse Width Modulation                 |

| SRF-PLL             | Synchronous Reference Frame PLL                   |

| STC                 | Standard Test Conditions                          |

| STSMO               | Super-Twisting Sliding Mode Observer              |

| SVM                 | Space Vector Modulation                           |

| 3D-SVM / 3DSVPWM    | Three-Dimensional Space Vector Modulation / PWM   |

| THD                 | Total Harmonic Distortion                         |

| TOSM                | Third-Order Sliding Mode                          |

| VCO                 | Voltage-Controlled Oscillator                     |

| VOC                 | Voltage-Oriented Control                          |

| VSI                 | Voltage Source Inverter                           |

| ZS                  | Zero-Sequence                                     |

| <b>Abbreviation</b> | <b>Full Form</b>                  |

|---------------------|-----------------------------------|

| ZSC                 | Zero-Sequence Current             |

| ZSCC                | Zero-Sequence Circulating Current |

| ZSDR                | Zero-Sequence Duty Ratio          |

| ZSV                 | Zero-Sequence Voltage             |

| ZV                  | Zero Vector                       |

| 4LI                 | Four-Leg Inverter                 |

| $\alpha\beta0$      | Alpha-Beta-Zero (reference frame) |

### **Lists of Figures**

| <b>Figure Number</b> | <b>Caption</b>                                                                                   | <b>Page</b> |

|----------------------|--------------------------------------------------------------------------------------------------|-------------|

| Figure I.1           | Formation of the Transition Region in a PN Junction                                              | 8           |

| Figure I.2           | Light Absorption and Energy Transfer from Photons to Electrons                                   | 9           |

| Figure I.3           | Photovoltaic cell's P-N junction and N- and P-                                                   | 10          |

| Figure I.4           | Silicon crystalline PV module: monocrystalline (a), polycrystalline (b)                          | 11          |

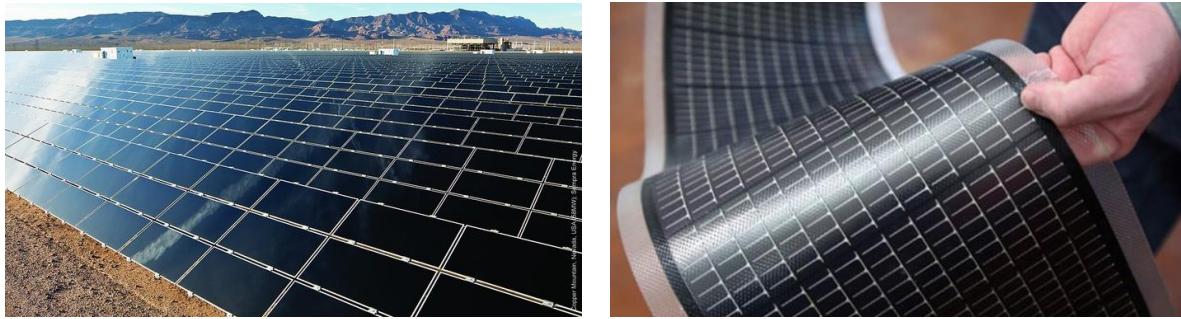

| Figure I.5           | Thin-film PV module                                                                              | 12          |

| Figure I.6           | Perovskites PV solar cell                                                                        | 12          |

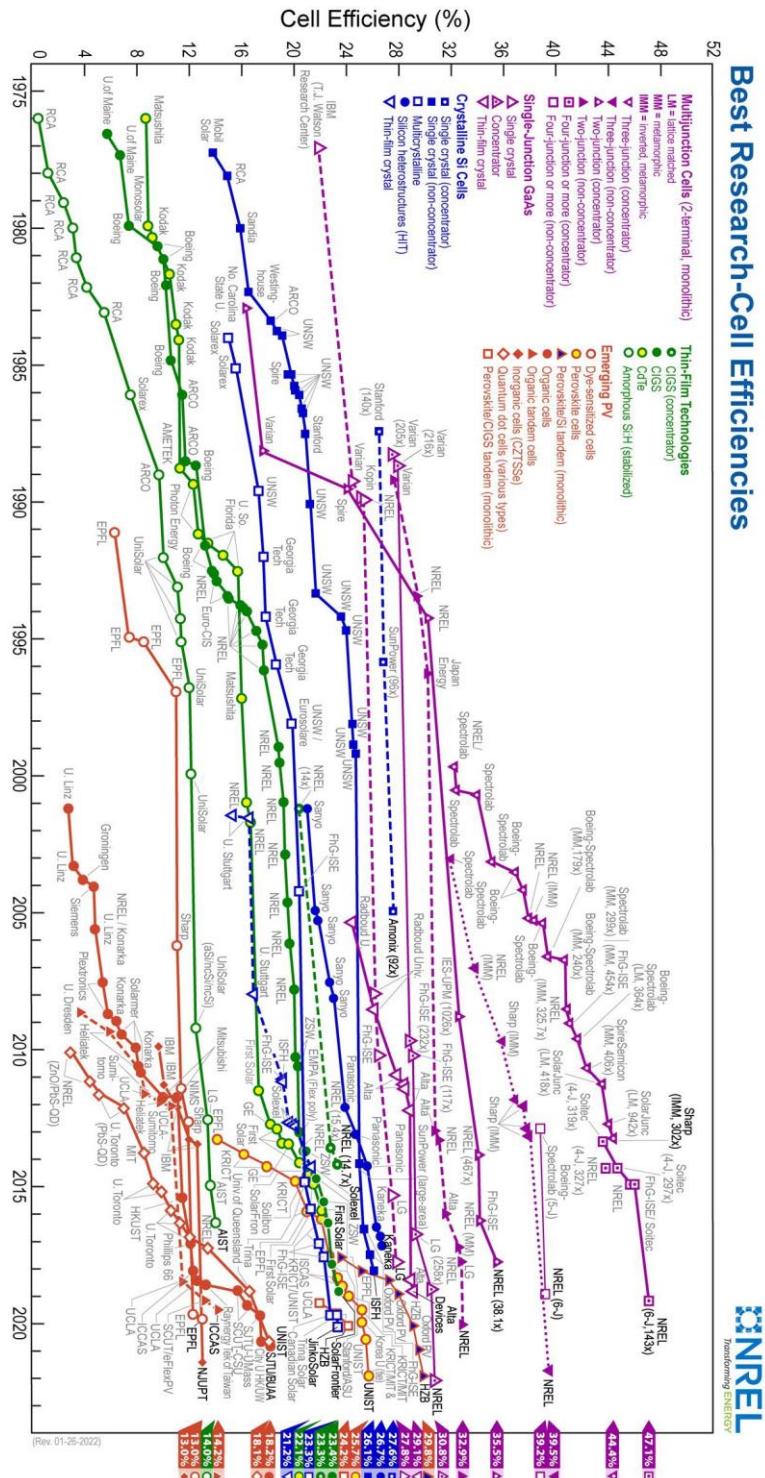

| Figure I.7           | Chart of best research-cell efficiencies from 1976 to 2022 provided by NRLE                      | 13          |

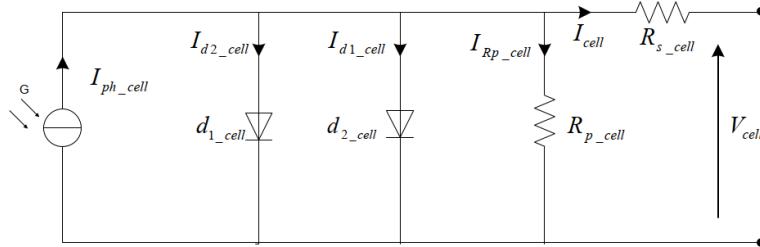

| Figure I.8           | Equivalent Circuit of the Two-Diode Model for a Photovoltaic Cell                                | 14          |

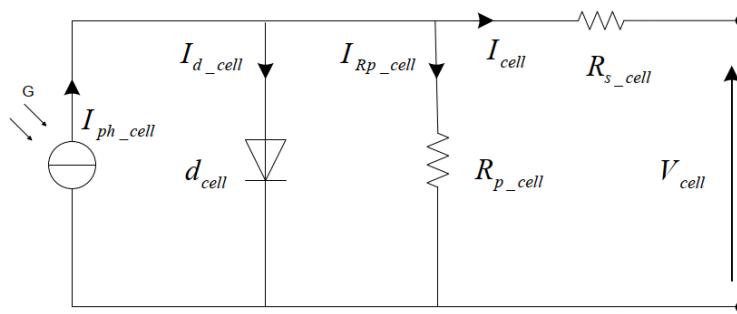

| Figure I.9           | Equivalent Circuit of the Single-Diode Model for a Photovoltaic Cell                             | 15          |

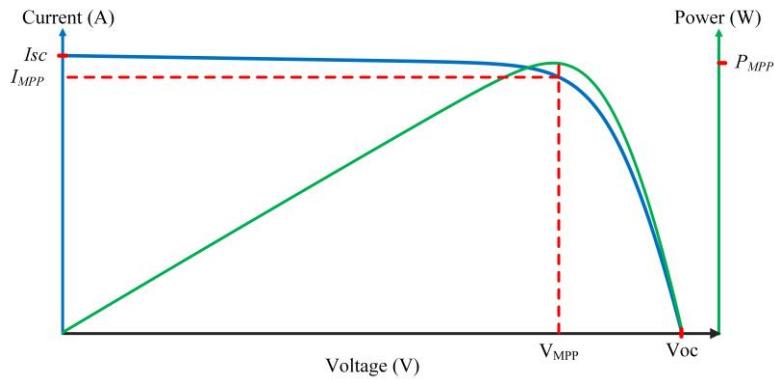

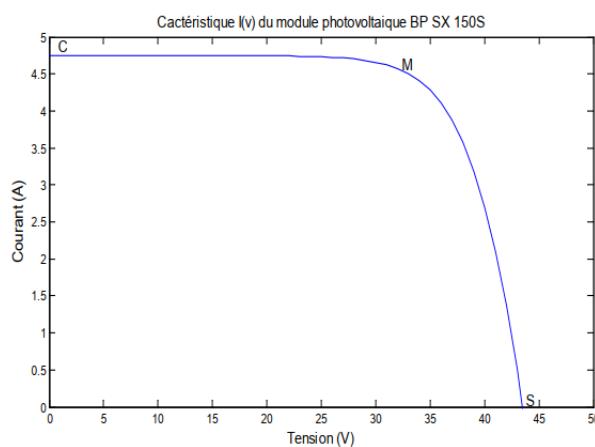

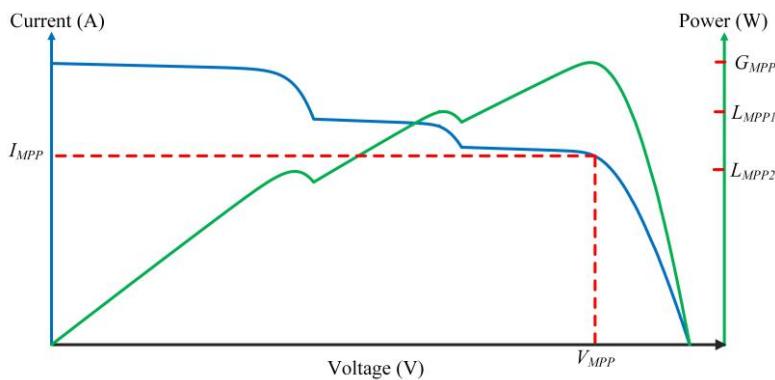

| Figure I.10          | The electrical characteristic I-V and P-V curves of the PV module                                | 16          |

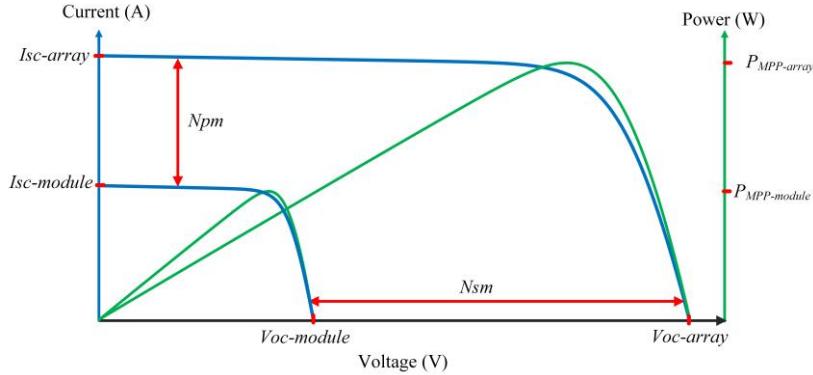

| Figure I.11          | The electrical characteristic of the PV array                                                    | 17          |

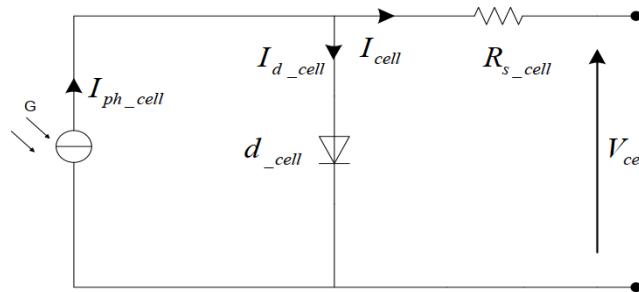

| Figure I.12          | Equivalent Circuit of the Photovoltaic Cell Model with Ohmic Losses                              | 17          |

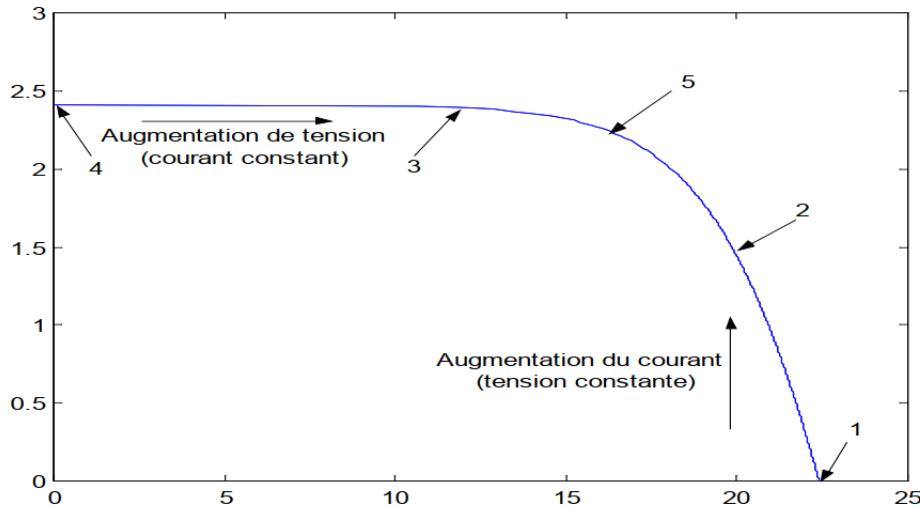

| Figure I.13          | Typical I-V Characteristic Curve of a Solar Cell                                                 | 21          |

| Figure I.14          | PV system configuration: string (a), array (b)                                                   | 23          |

| Figure I.15          | Photovoltaic modules connected in series and parallel                                            | 23          |

| Figure I.16          | Photovoltaic Module                                                                              | 24          |

| Figure I.17          | Equivalent circuit of a photovoltaic module (panel) model                                        | 24          |

| Figure I.18          | Current-Voltage Characteristic of a Photovoltaic Module                                          | 26          |

| Figure I.19          | I-V and P-V curves of a panel under varying sunlight conditions. (a) I-V curves, (b) P-V curves  | 27          |

| Figure I.20          | I-V and P-V Curves of a Photovoltaic Module at Various Temperatures ( $G = 1000 \text{ W/m}^2$ ) | 27          |

| Figure I.21          | Effect of Series Resistance on the I-V and P-V Characteristic of a PV Module                     | 28          |

| Figure I.22          | Partial shading impact on I-V curve (a), P-V curve (b)                                           | 28          |

| Figure I.23          | Photovoltaic modules connected in series and parallel                                            | 29          |

| Figure I.24          | Equivalent circuit of a PVG                                                                      | 29          |

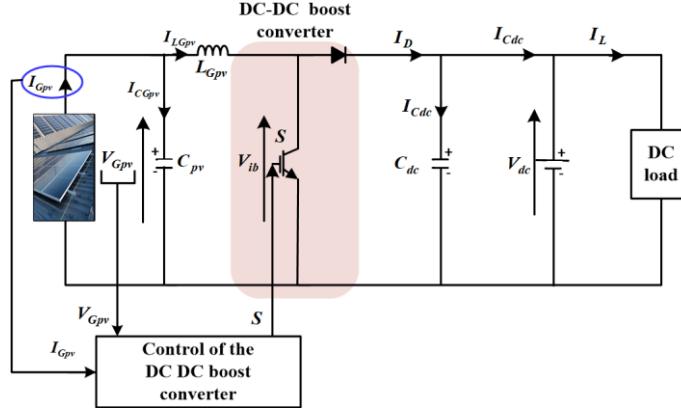

| Figure I.25          | Schematic diagram of the PVG DC-DC boost converter-based standalone power supply system          | 31          |

| <b>Figure Number</b> | <b>Caption</b>                                                                                                                                       | <b>Page</b> |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

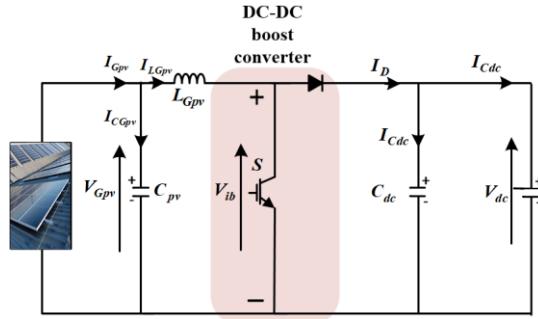

| Figure I.26          | Electrical circuit of a DC-DC boost converter-based PVG                                                                                              | 32          |

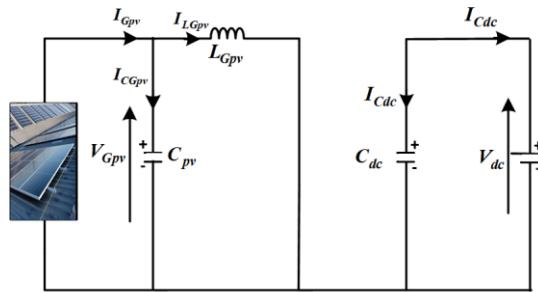

| Figure I.27          | Equivalent circuit of the boost converter when the switch S closed                                                                                   | 32          |

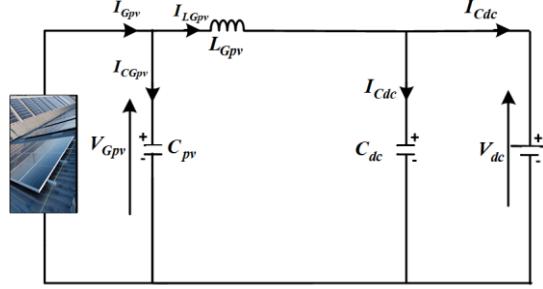

| Figure I.28          | Equivalent circuit of the boost converter when the switch S open                                                                                     | 33          |

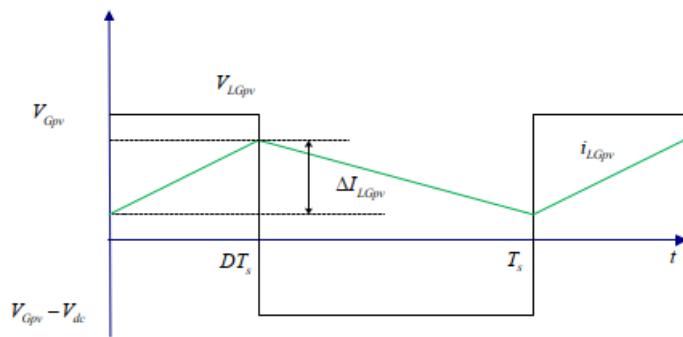

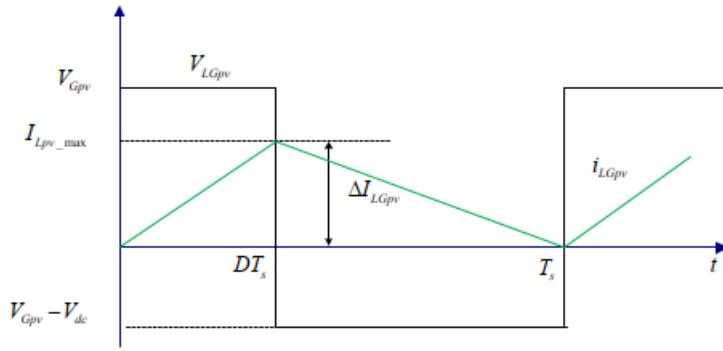

| Figure I.29          | Operating of boost converter in CCM                                                                                                                  | 33          |

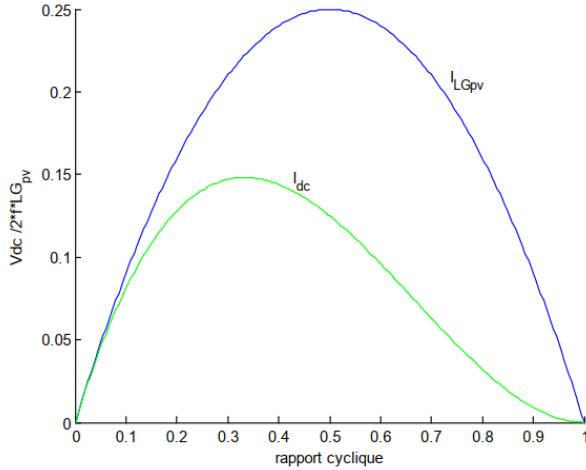

| Figure I.30          | Limit between continuous and discontinuous modes                                                                                                     | 34          |

| Figure I.31          | DC-DC boost converter's output current and inductor current at the limit between continuous and discontinuous modes under constant output DC voltage | 35          |

| Figure I.32          | Current/voltage waveforms of a boost converter in CCM                                                                                                | 36          |

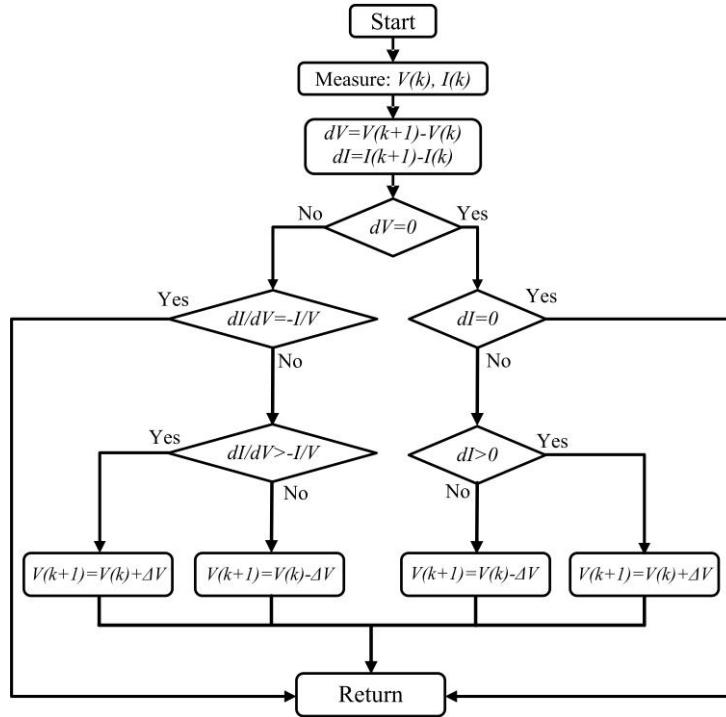

| Figure I.33          | Conventional P&O flow chart                                                                                                                          | 39          |

| Figure I.34          | The flow chart of the incremental conductance algorithm                                                                                              | 41          |

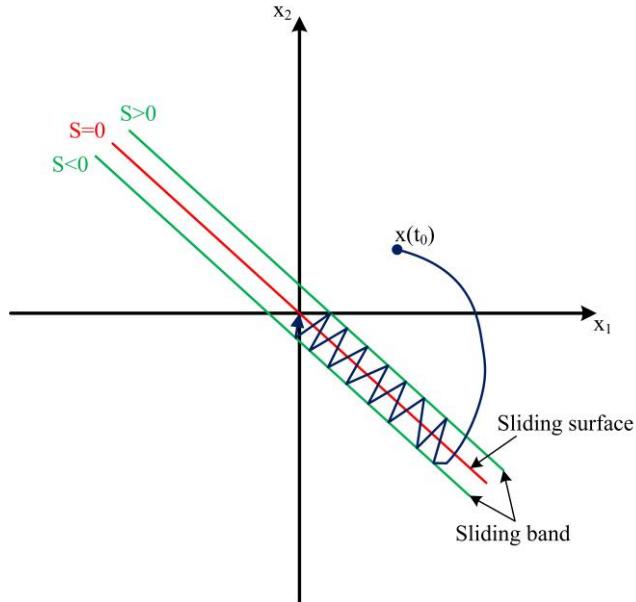

| Figure I.35          | Phase portrait of a first-order sliding mode controller                                                                                              | 42          |

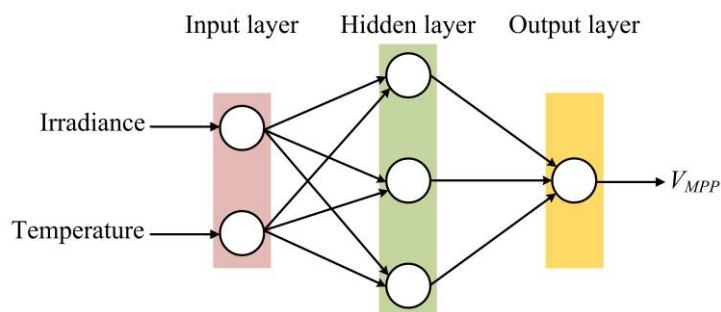

| Figure I.36          | Example of the structure of ANNs-based MPPT                                                                                                          | 42          |

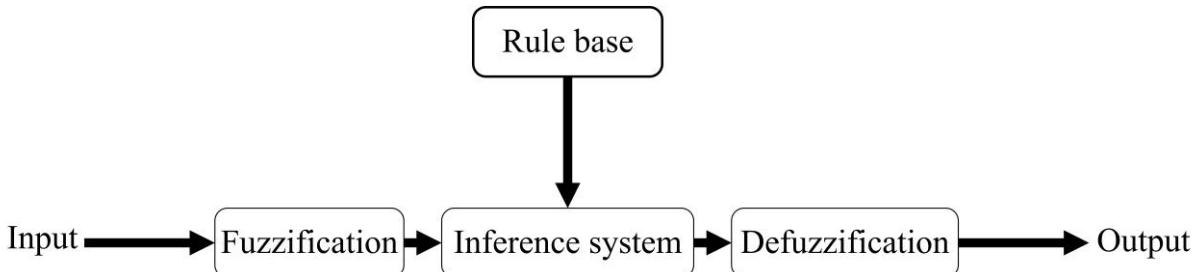

| Figure I.37          | Fuzzy logic controller's block diagram                                                                                                               | 43          |

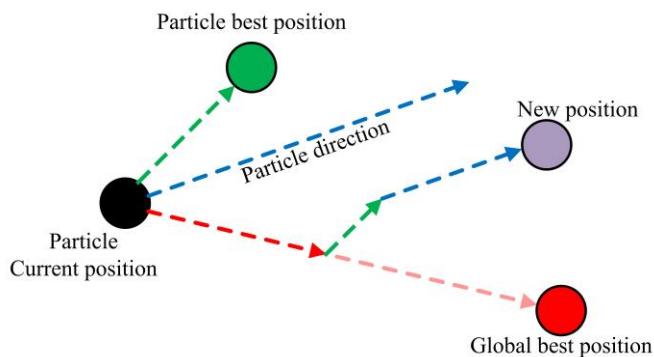

| Figure I.38          | Particle swarm optimization algorithm                                                                                                                | 43          |

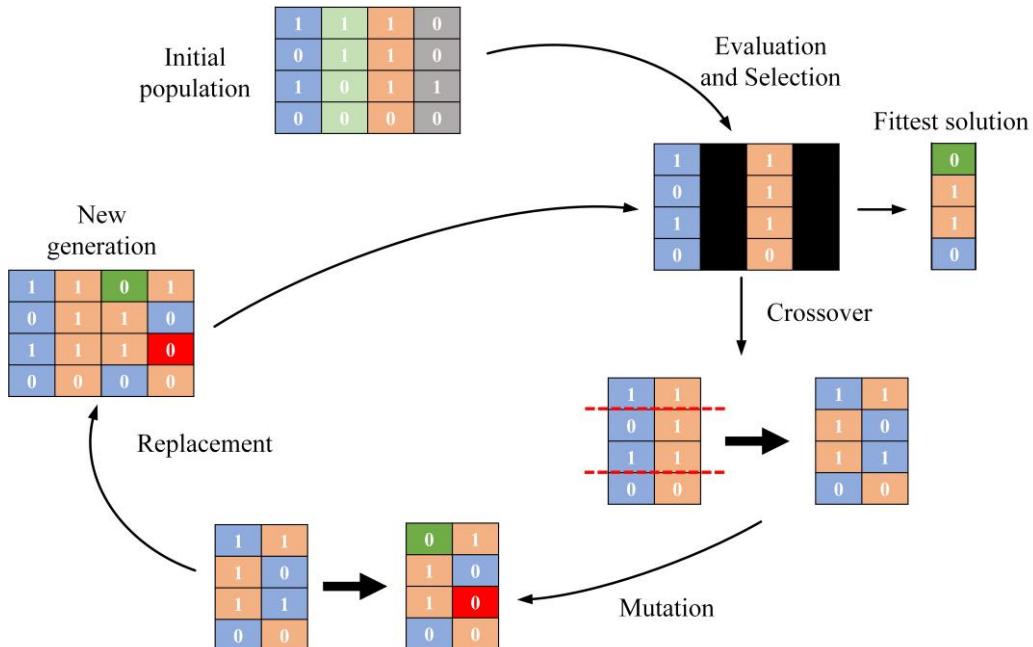

| Figure I.39          | The main steps of the genetic algorithm                                                                                                              | 44          |

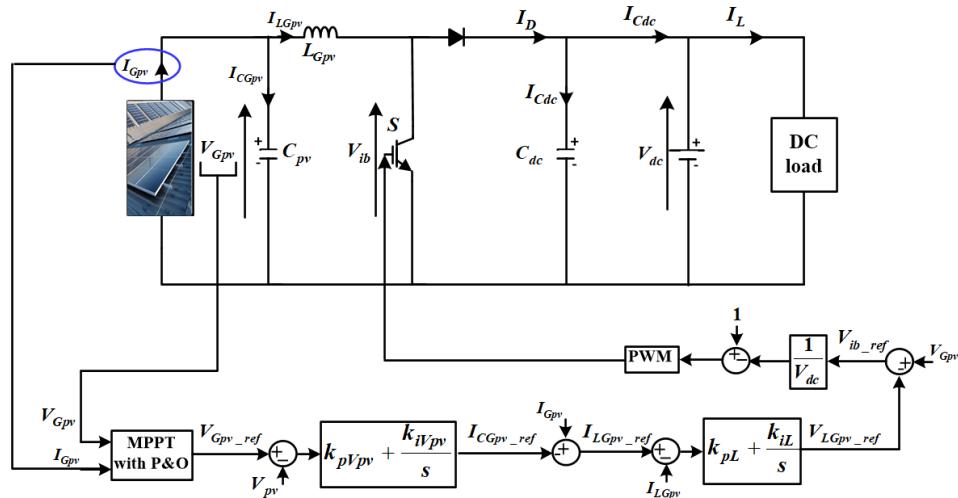

| Figure I.40          | Schematic diagram of the PI control of DC-DC boost converter-based standalone power supply system                                                    | 45          |

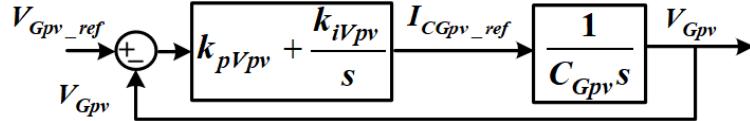

| Figure I.41          | Schematic diagram of the PI-based PVG output voltage regulation                                                                                      | 47          |

| Figure I.42          | Schematic diagram of the PI-based DC-DC boost converter's input inductor current regulation                                                          | 47          |

| Figure II.1          | Circuit of the three-phase 4LI                                                                                                                       | 52          |

| Figure II.2          | Vectorial representation of the 4LI output voltages                                                                                                  | 55          |

| Figure II.3          | Schematic diagram of the PVG grid connected 4LI                                                                                                      | 56          |

| Figure II.4          | Four leg inverter's input DC capacitor                                                                                                               | 61          |

| Figure II.5          | Overall control diagram of the PV grid-connected 4LI for harmonic and reactive power compensation under nonlinear single phase loads                 | 62          |

| Figure II.6          | Schematic of the traditional PLL                                                                                                                     | 65          |

| Figure II.7          | Schematic detail of the traditional PLL                                                                                                              | 65          |

| Figure II.8          | Schematic detail of the RSPLL                                                                                                                        | 67          |

| Figure II.9          | Block diagram of the simplified reference determinations method using instantaneous real, imaginary, and ZS power                                    | 70          |

| Figure II.10         | Block diagram of the DC bus voltage regulation using PI controller                                                                                   | 71          |

| Figure II.11         | Block diagram of the inner 4LI's output currents control loop in the dq0 reference frame using PI controllers                                        | 72          |

| Figure II.12         | Block diagram of the 4LI's output current regulations using PI controllers                                                                           | 73          |

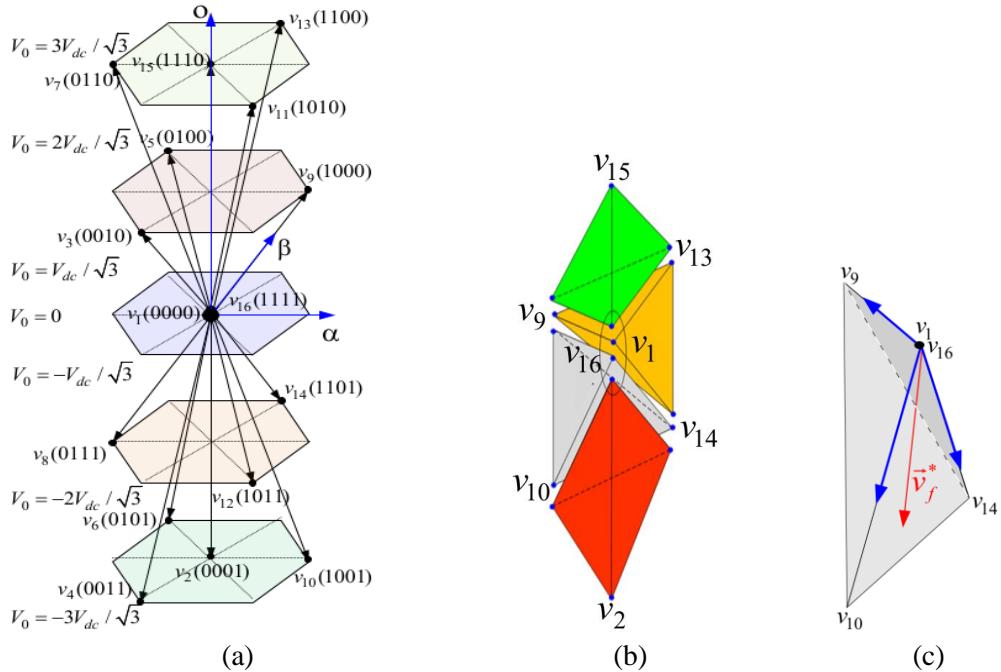

| Figure II.13         | Vectorial representation of voltages generated by the four-leg two-level inverter                                                                    | 74          |

| Figure II.14         | Representation of different prisms                                                                                                                   | 74          |

| Figure II.15         | Flowchart of prism identification operations                                                                                                         | 75          |

| <b>Figure Number</b> | <b>Caption</b>                                                                                                                                                                                                                                           | <b>Page</b> |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure II.16         | Representation of the four tetrahedra (Tet1, Tet2, Tet3, Tet4) in prism 1 and the three non-zero state vectors in each tetrahedron                                                                                                                       | 75          |

| Figure II.17         | Represents the physical positions of the voltage vectors in each prism and in each tetrahedron                                                                                                                                                           | 77          |

| Figure II.18         | Representation of the equations of the planes of tetrahedron 1 of prism I                                                                                                                                                                                | 79          |

| Figure II.19         | Projection of the reference vector onto the adjacent vectors                                                                                                                                                                                             | 80          |

| Figure II.20         | Shapes of the switching functions $F_j$ for the four tetrahedra of the first prism in three-dimensional vector modulation control (3DSVM)                                                                                                                | 83          |

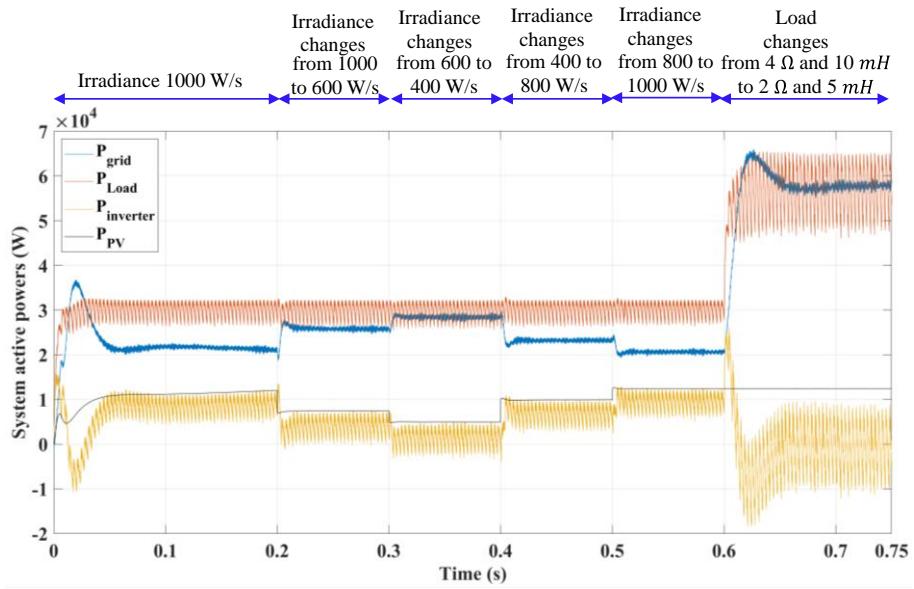

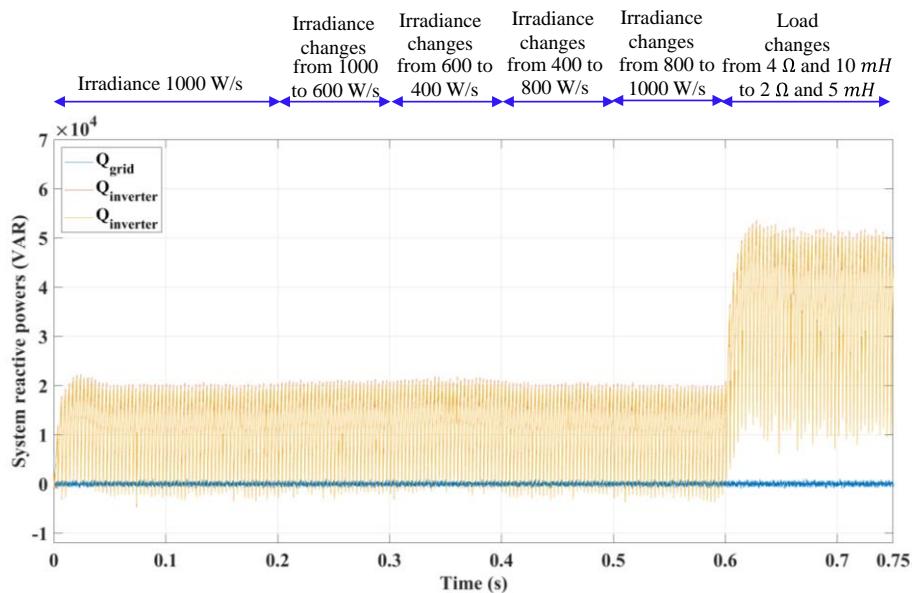

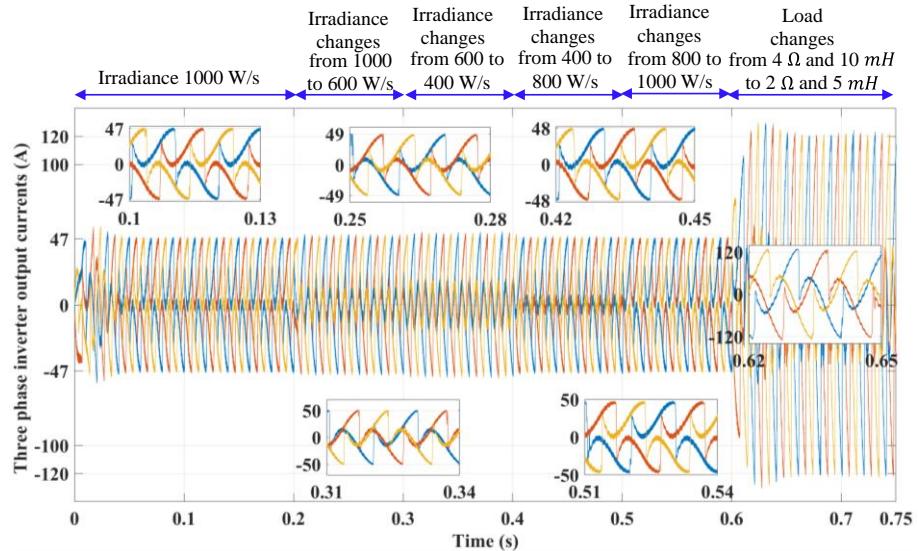

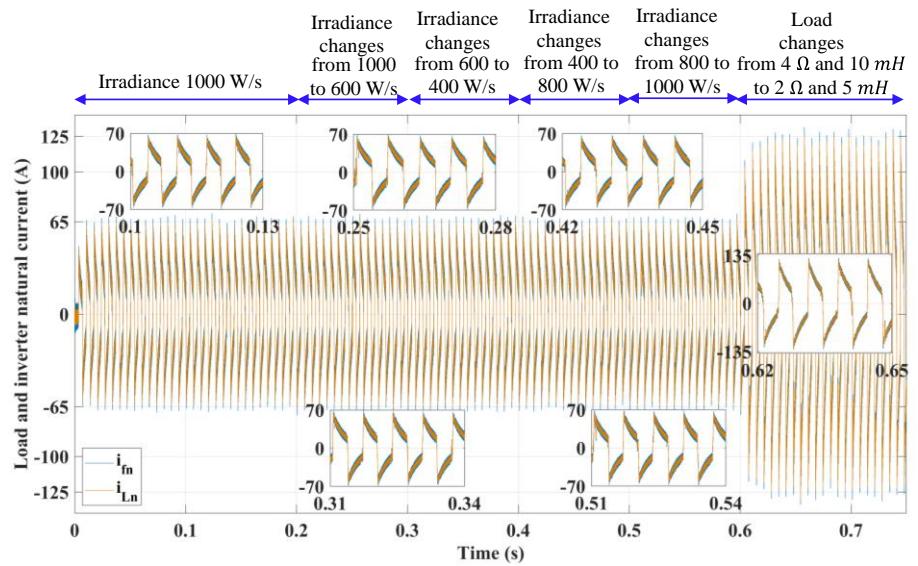

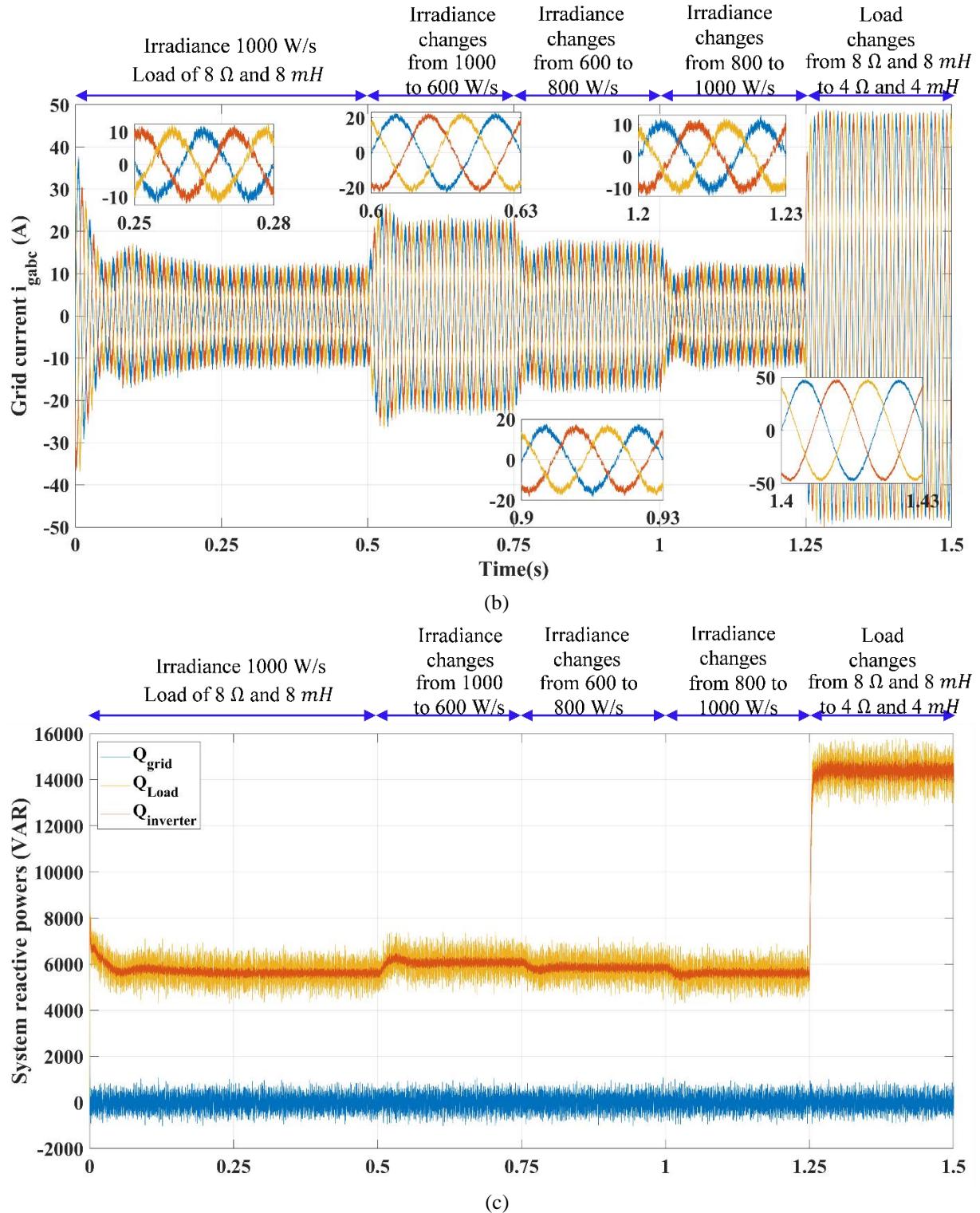

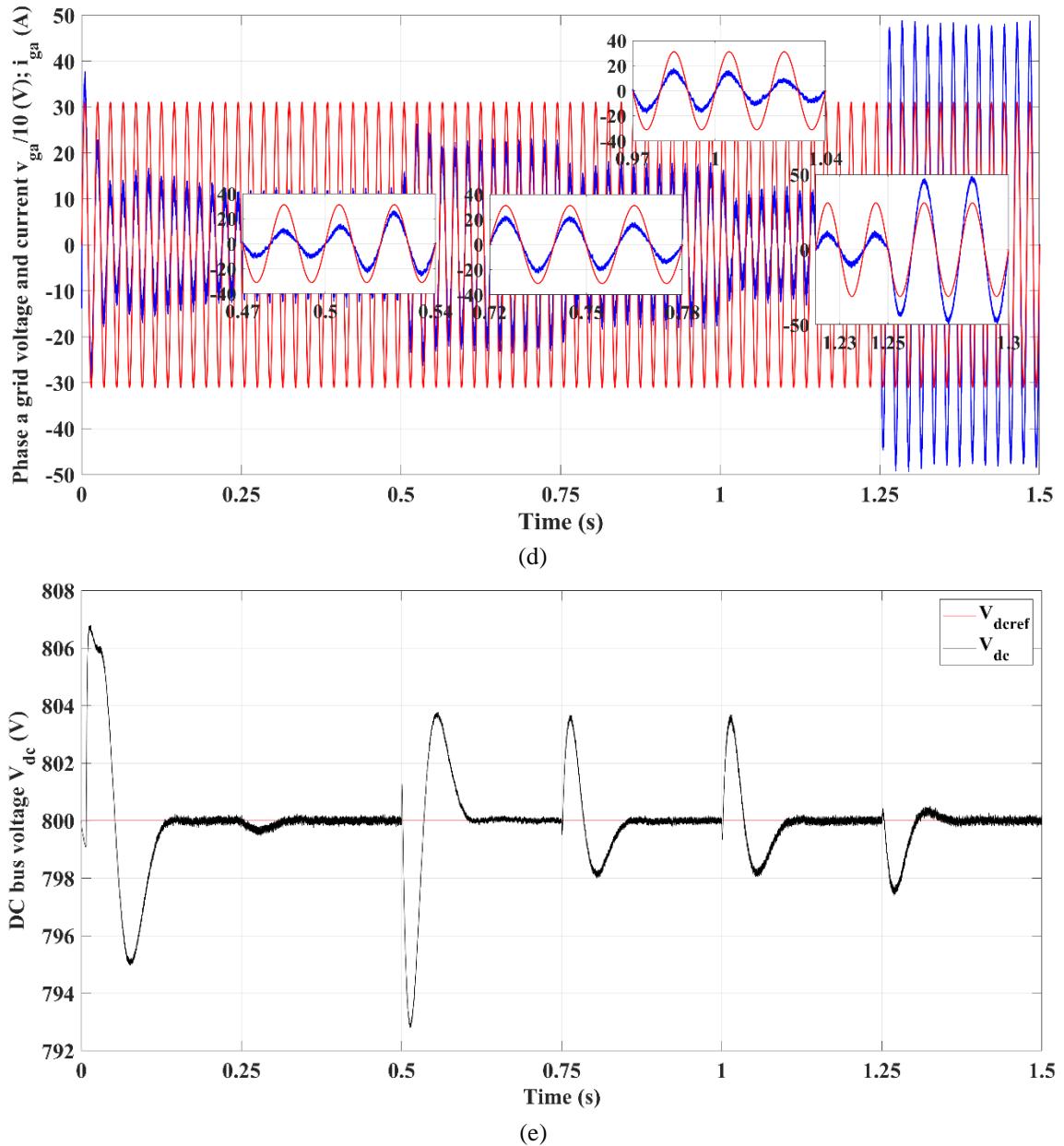

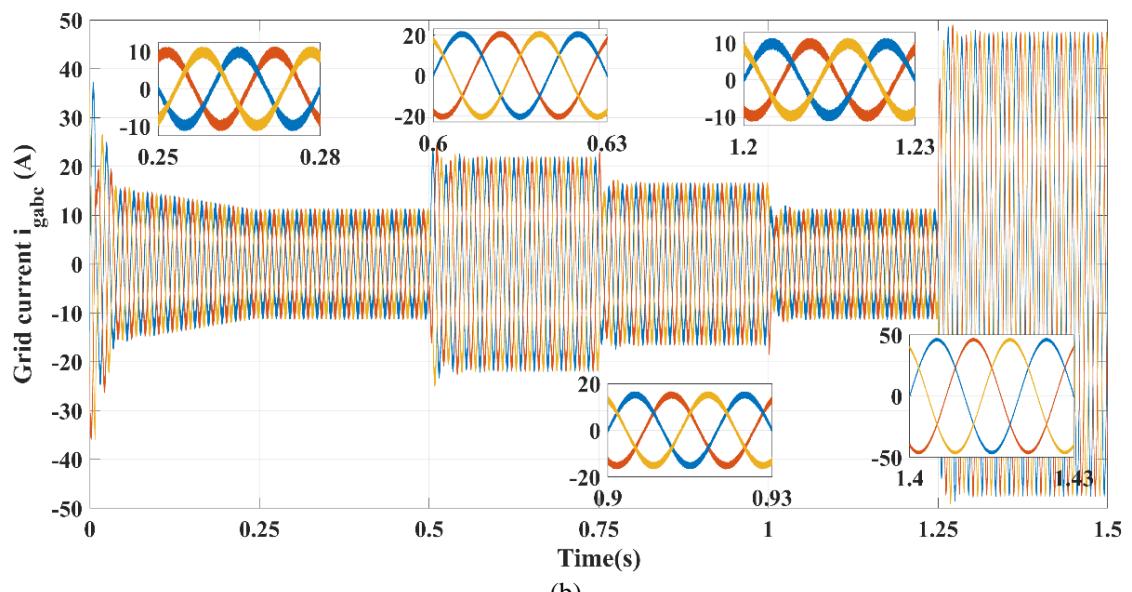

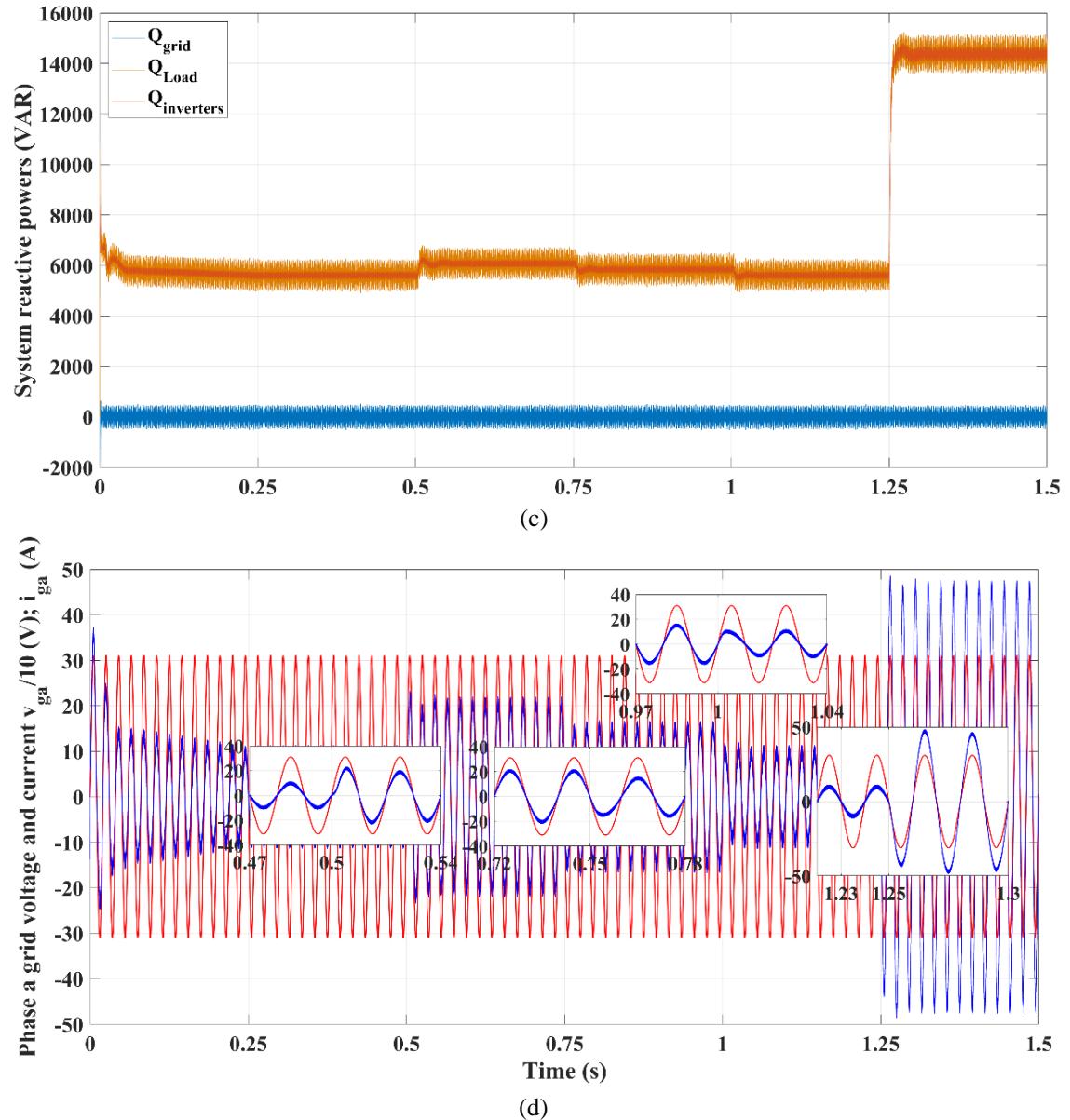

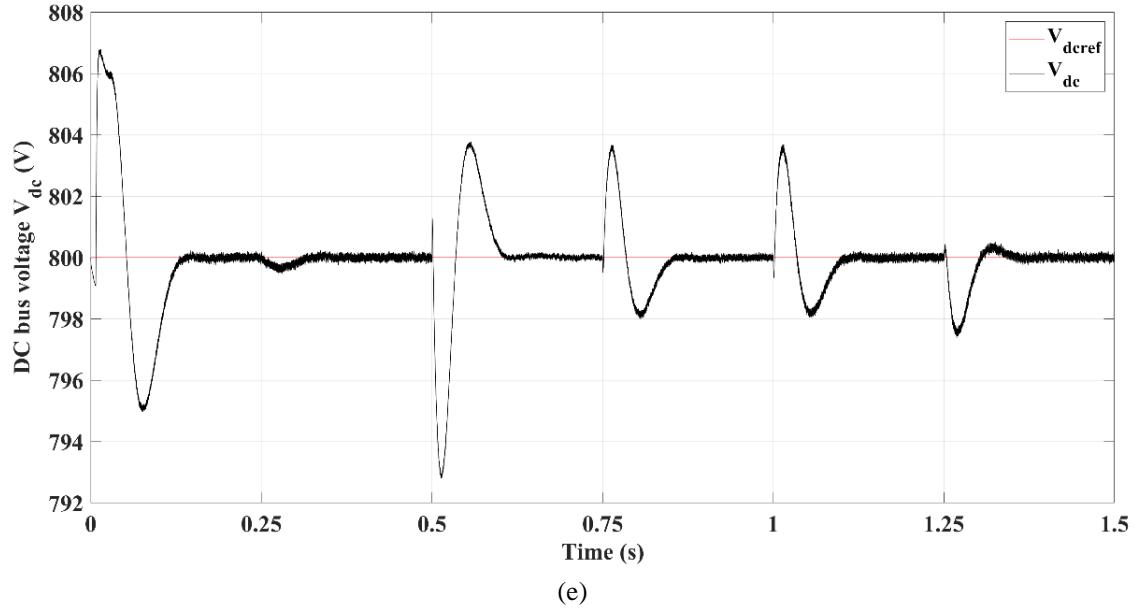

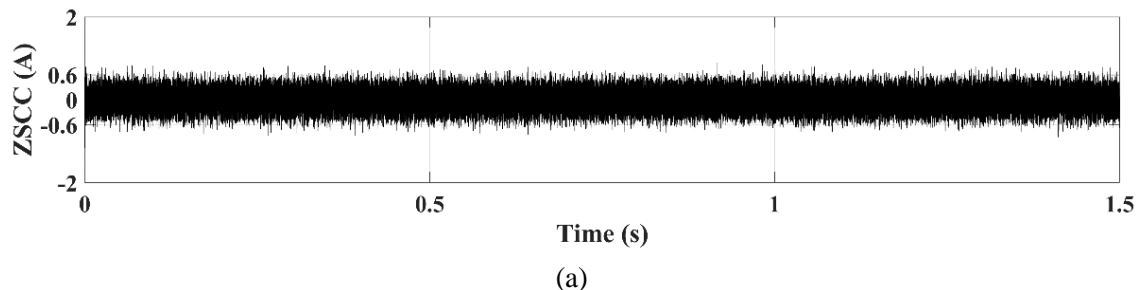

| Figure II.21         | Performance of the overall system under sudden changes in solar irradiance and single phase nonlinear loads (subfigures a-j)                                                                                                                             | 86-89       |

| Figure II.22         | Overall control diagram of the PV grid-connected 4LI system for reactive power compensation under three phase linear load                                                                                                                                | 90          |

| Figure II.23         | PV grid connected four leg inverter system active powers                                                                                                                                                                                                 | 93          |

| Figure II.24         | PV grid connected four leg inverter system powers                                                                                                                                                                                                        | 93          |

| Figure II.25         | Four leg inverter output three phase currents                                                                                                                                                                                                            | 94          |

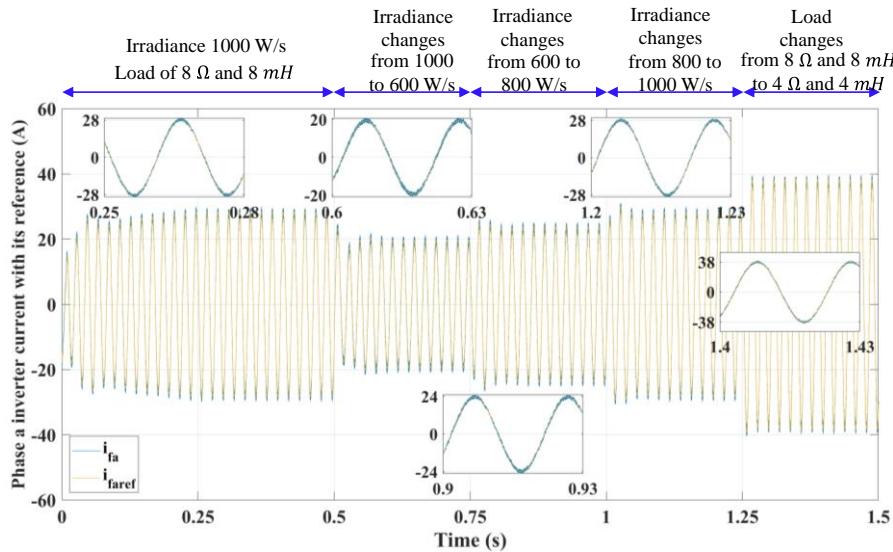

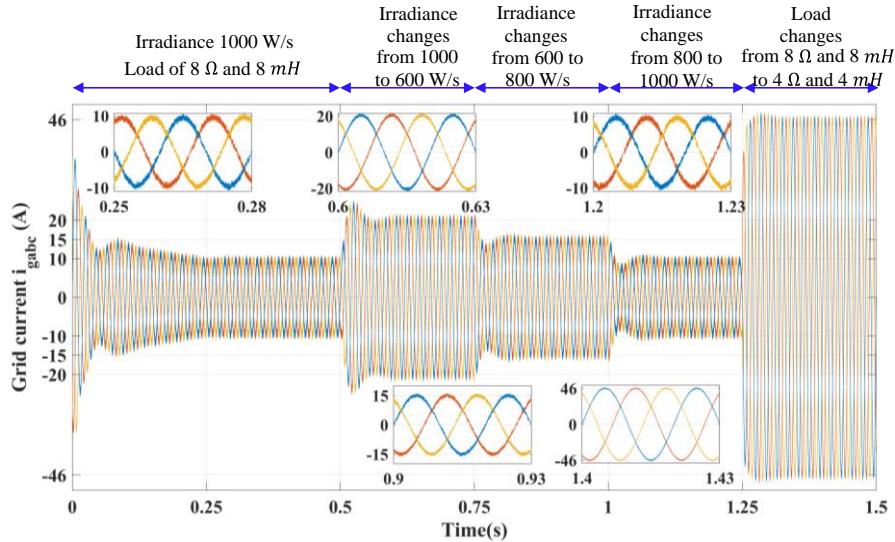

| Figure II.26         | Phase a of Four leg inverter output current with its reference                                                                                                                                                                                           | 94          |

| Figure II.27         | Spectrum harmonic of first phase inverter's output current. (a) In zone of lower amplitude [0.5 0.75 s], (b) In zone of high amplitude [1.25 1.5 s]                                                                                                      | 94          |

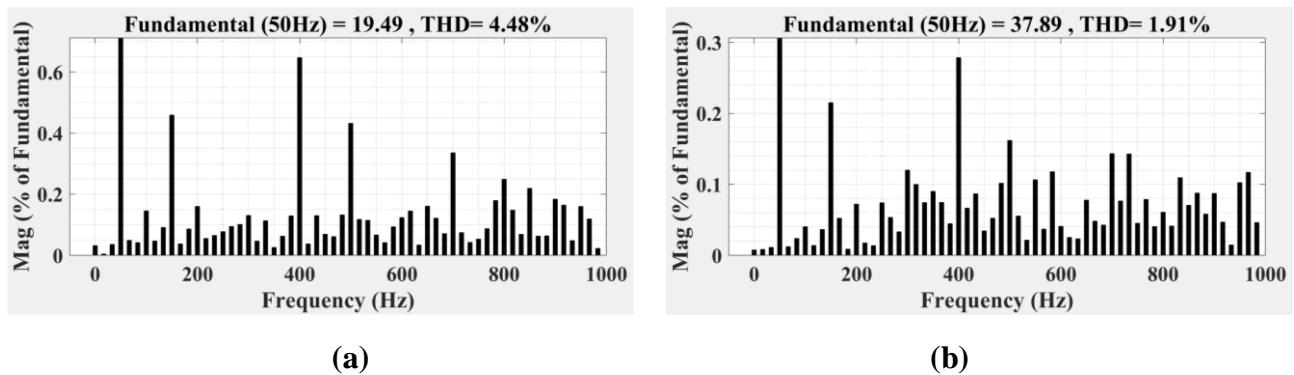

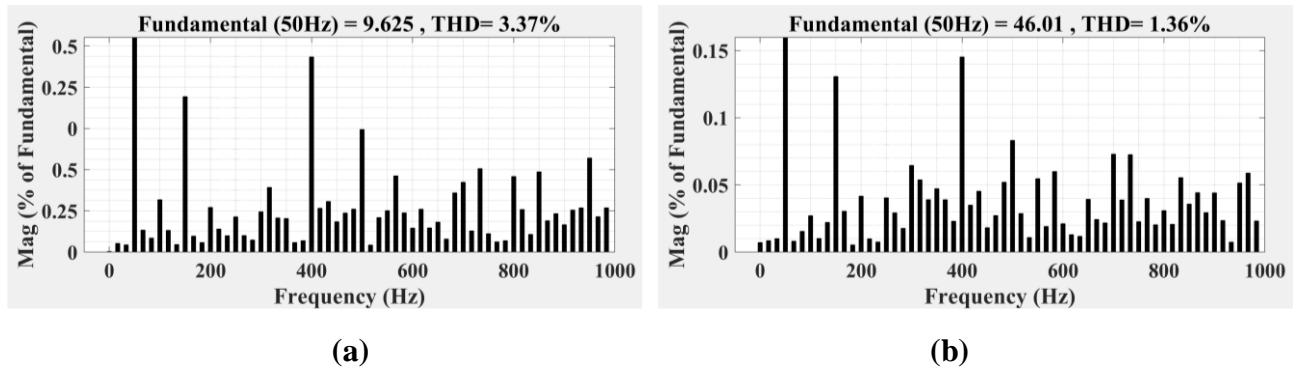

| Figure II.28         | Three phase grid currents                                                                                                                                                                                                                                | 95          |

| Figure II.29         | Spectrum harmonic of first phase grid current. (a) In zone of lower amplitude [0.5 0.75 s], (b) In zone of high amplitude [1.25 1.5 s]                                                                                                                   | 95          |

| Figure II.30         | First phase grid current with its corresponding voltage                                                                                                                                                                                                  | 95          |

| Figure II.31         | DC bus voltage                                                                                                                                                                                                                                           | 96          |

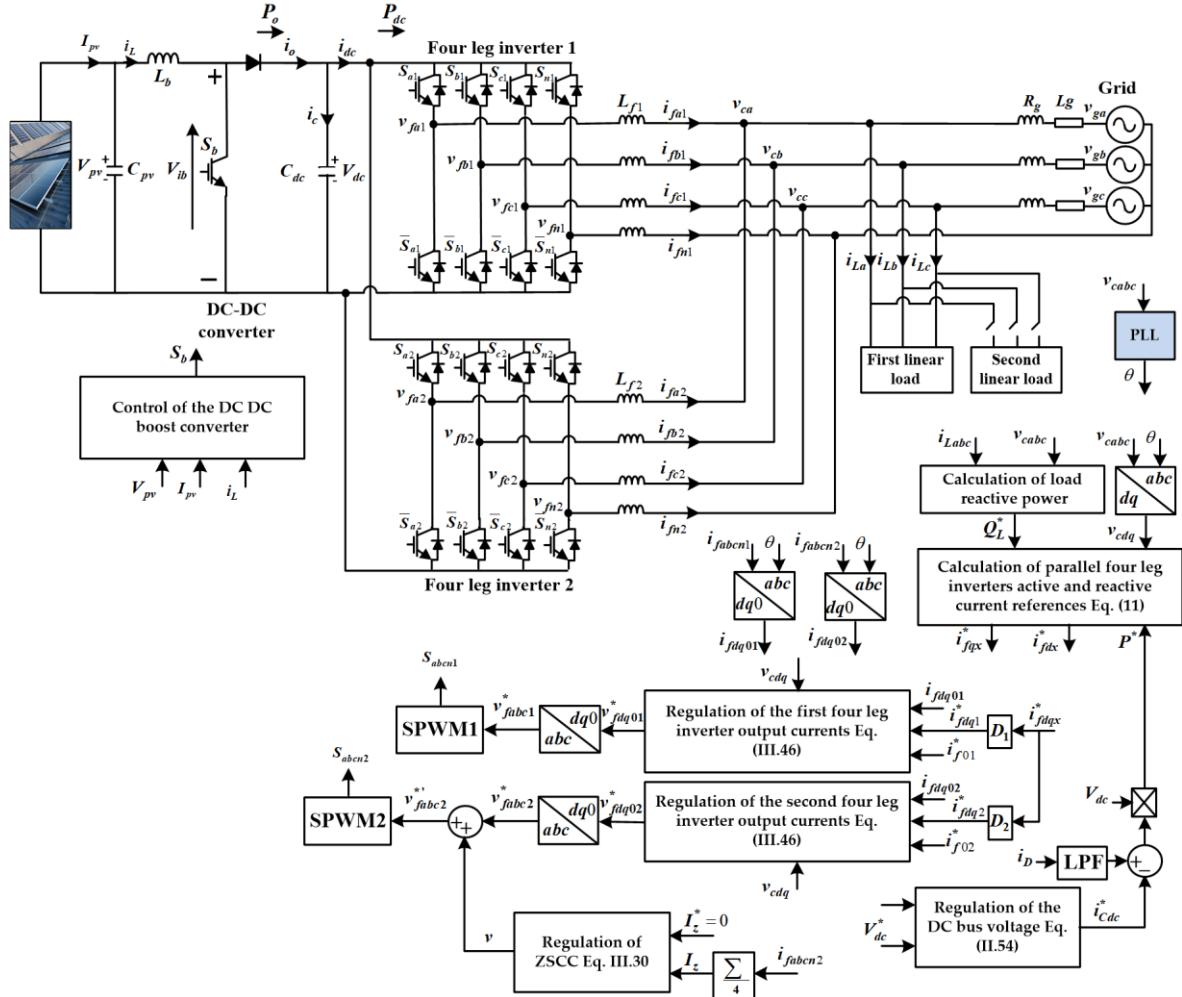

| Figure III.1         | Topologies of the PV grid connected parallel 4LI's system                                                                                                                                                                                                | 102         |

| Figure III.2         | Equivalent circuit of two parallel 4LIs in abc frame                                                                                                                                                                                                     | 103         |

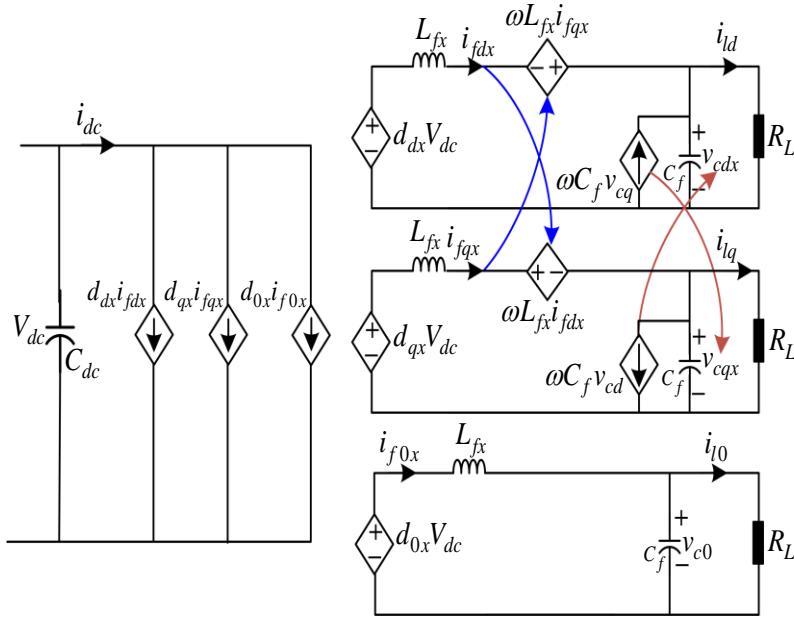

| Figure III.3         | Average equivalent circuit model of the two parallel 4LIs in the dq0 frame                                                                                                                                                                               | 105         |

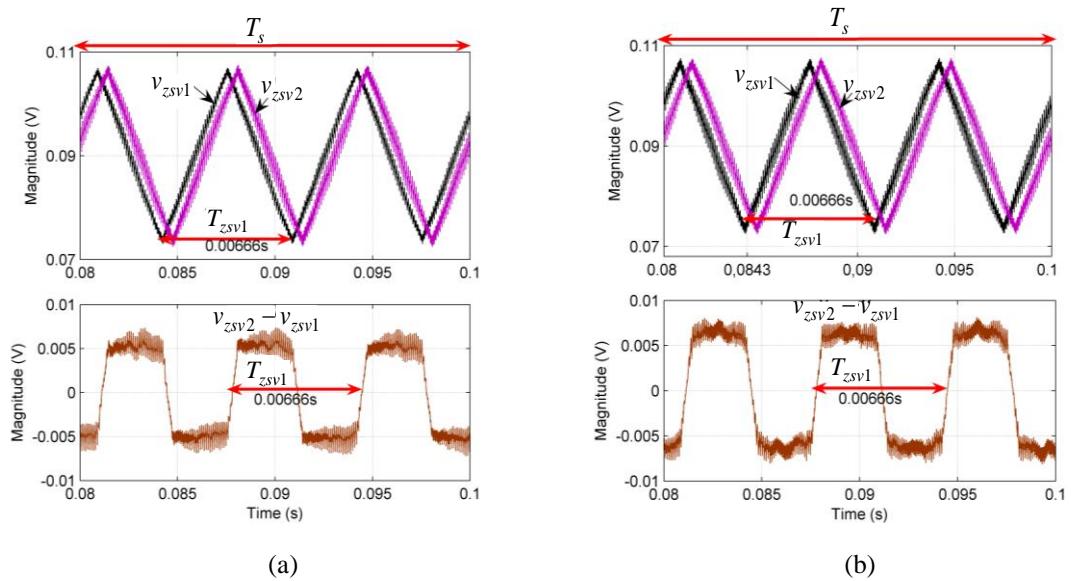

| Figure III.4         | ZSVs and their corresponding differences for parallel 4LIs operating with a modulation index of $m=1.0$ and a grid voltage frequency of $f=50$ Hz; (a) scenario with mismatched filter inductances, and (b) scenario with unequal output current sharing | 107         |

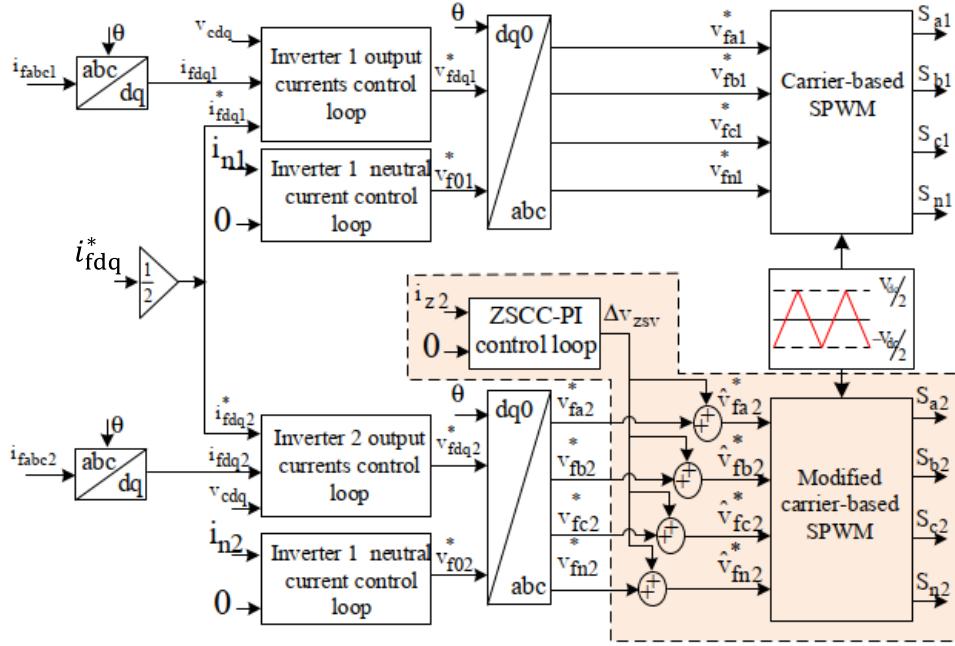

| Figure III.5         | Control of the parallel 4LIs using the adjusted PWM reference modulation voltages-based SPWM                                                                                                                                                             | 109         |

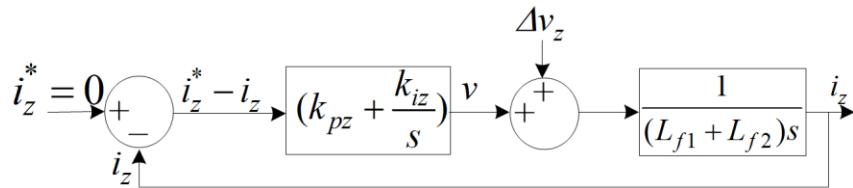

| Figure III.6         | Block diagram of the PI-based ZSCC regulation                                                                                                                                                                                                            | 110         |

| Figure III.7         | Four-leg inverter voltage vector's distributions; a) 3-D space vector diagram ( $\alpha\beta0$ ), b) tetrahedrons within prism 1, and c) tetrahedron1within prism1 and their voltage vectors                                                             | 111         |

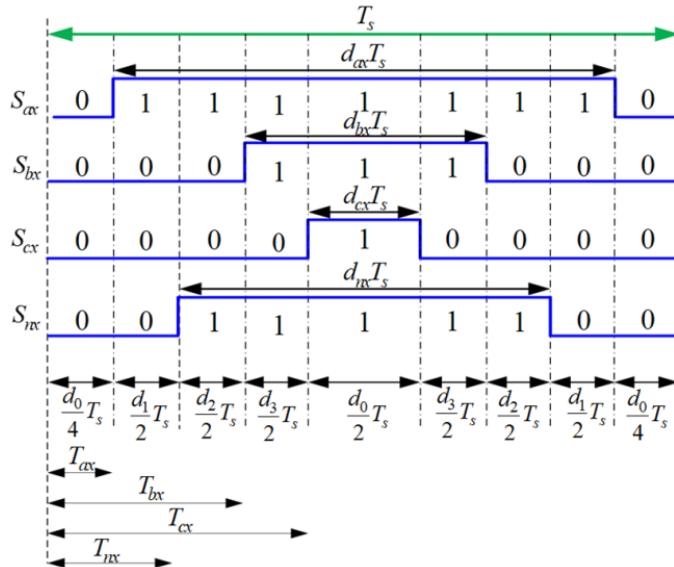

| Figure III.8         | Distribution of the active and zero vectors along with their corresponding duty ratios within each switching interval in the traditional 3DSVPWM method                                                                                                  | 112         |

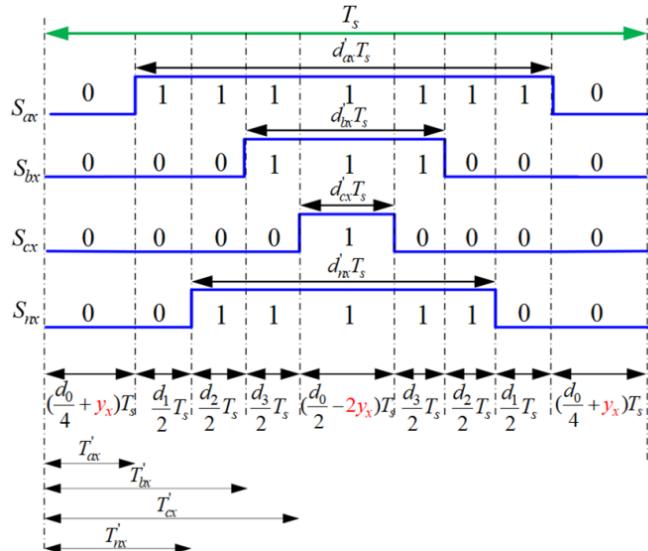

| Figure III.9         | Distribution of the active and zero vectors along with their corresponding duty ratios in the proposed adjusted 3DSVPWM                                                                                                                                  | 114         |

| <b>Figure Number</b> | <b>Caption</b>                                                                                                                                                                                                                                                                                                                       | <b>Page</b> |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

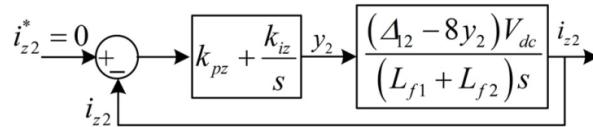

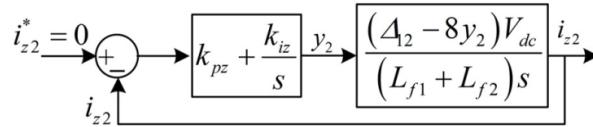

| Figure III.10        | Bloc diagram of the PI regulator for the ZSCC within the proposed adjusted 3D-SVPWM approach                                                                                                                                                                                                                                         | 115         |

| Figure III.11        | Control block diagram of the PV grid connected parallel 4LI system based reactive power compensation using the adjusted modulation voltage references-based SPWM technique                                                                                                                                                           | 116         |

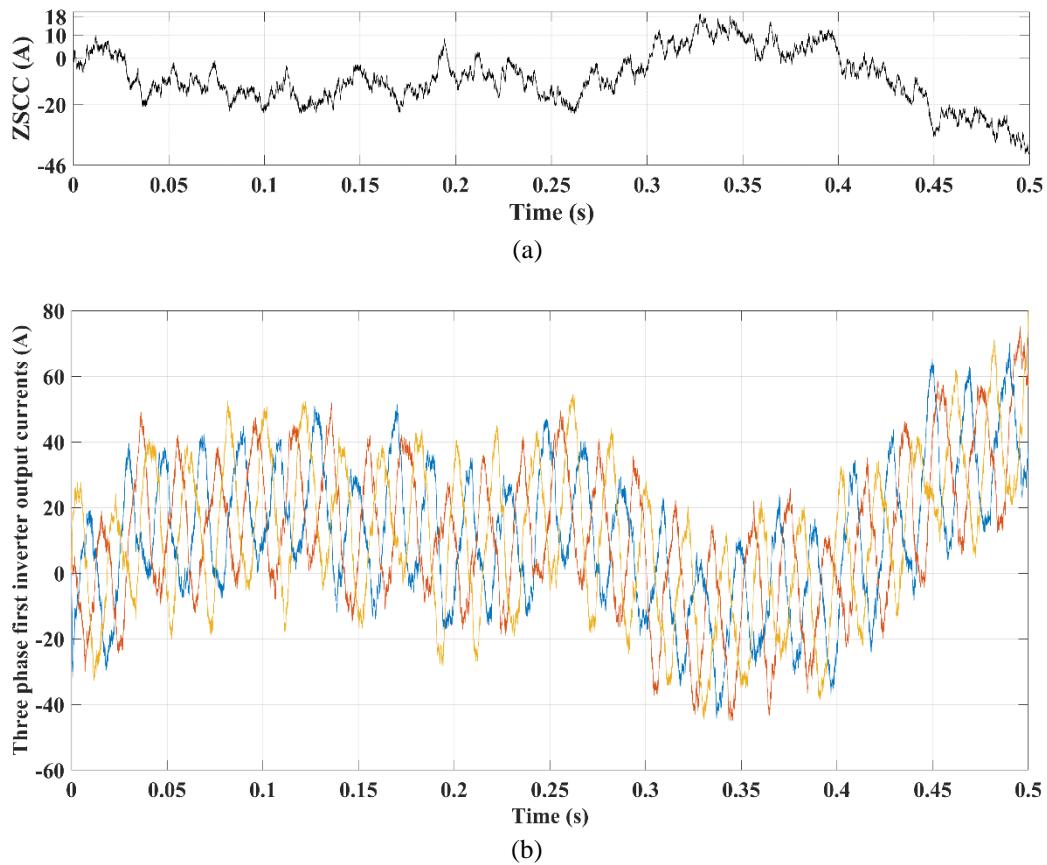

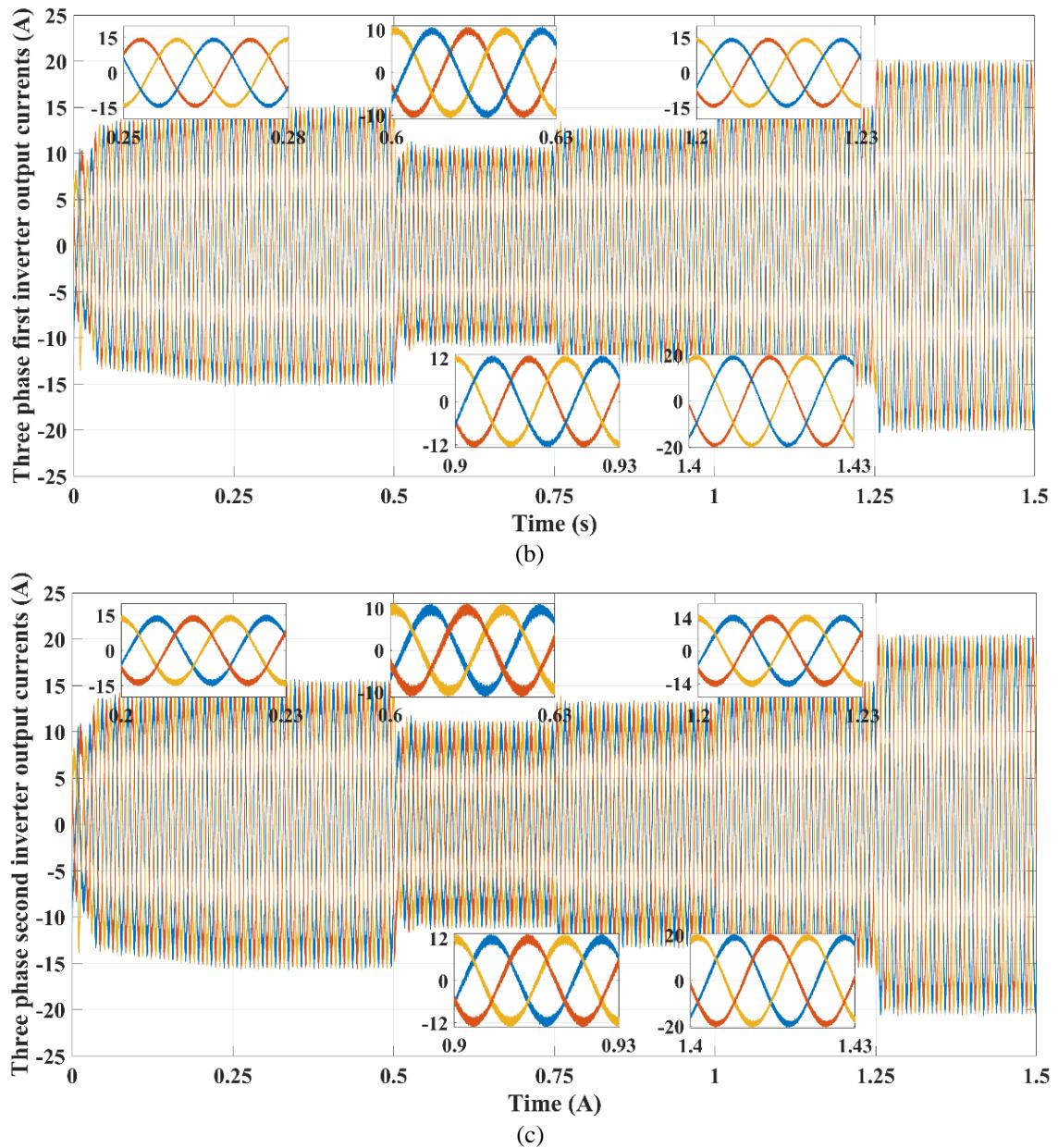

| Figure III.12        | Performance of the system controlled using the traditional SPWM under difference in output filter inductance values (subfigures a-d)                                                                                                                                                                                                 | 118-119     |

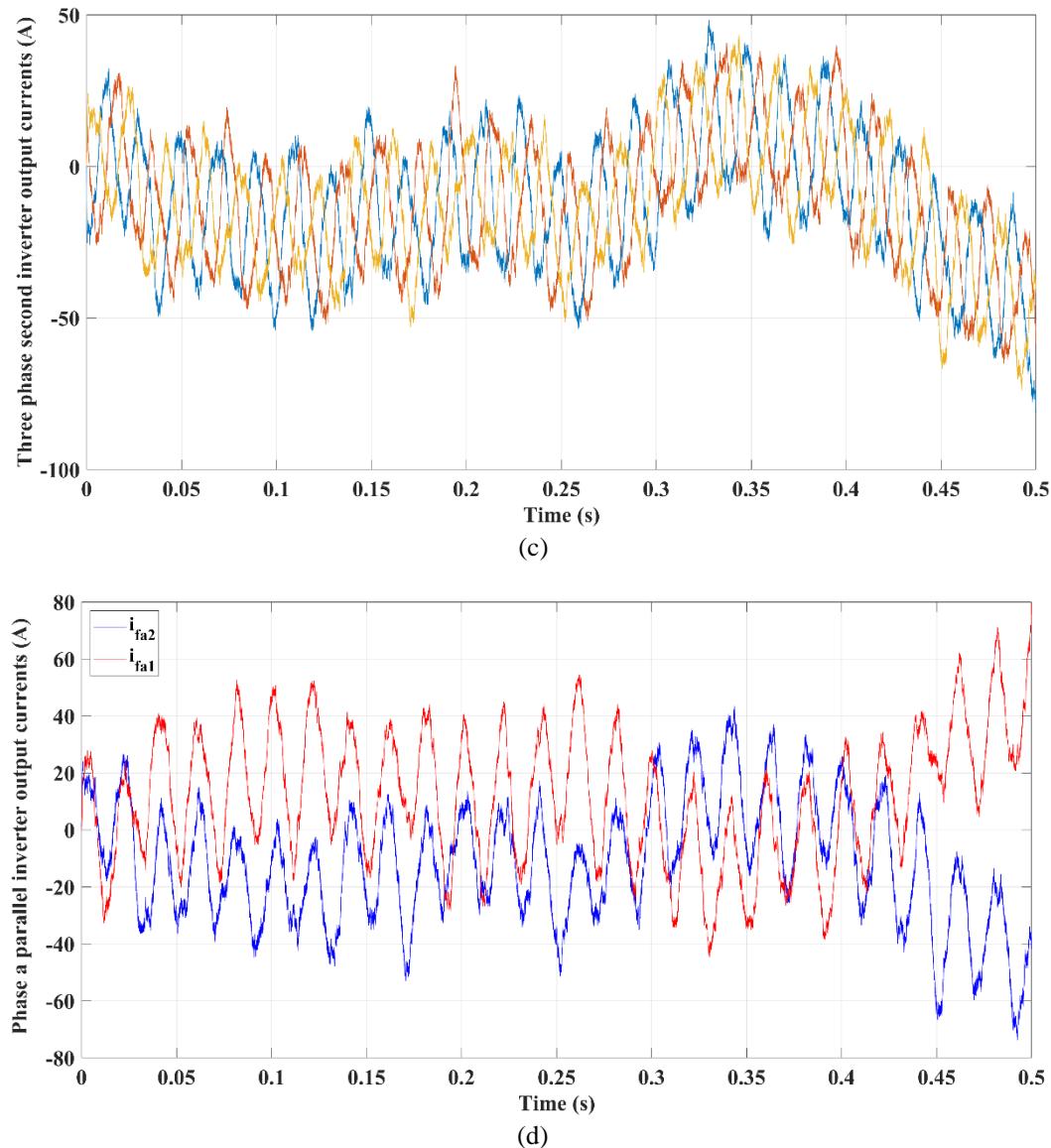

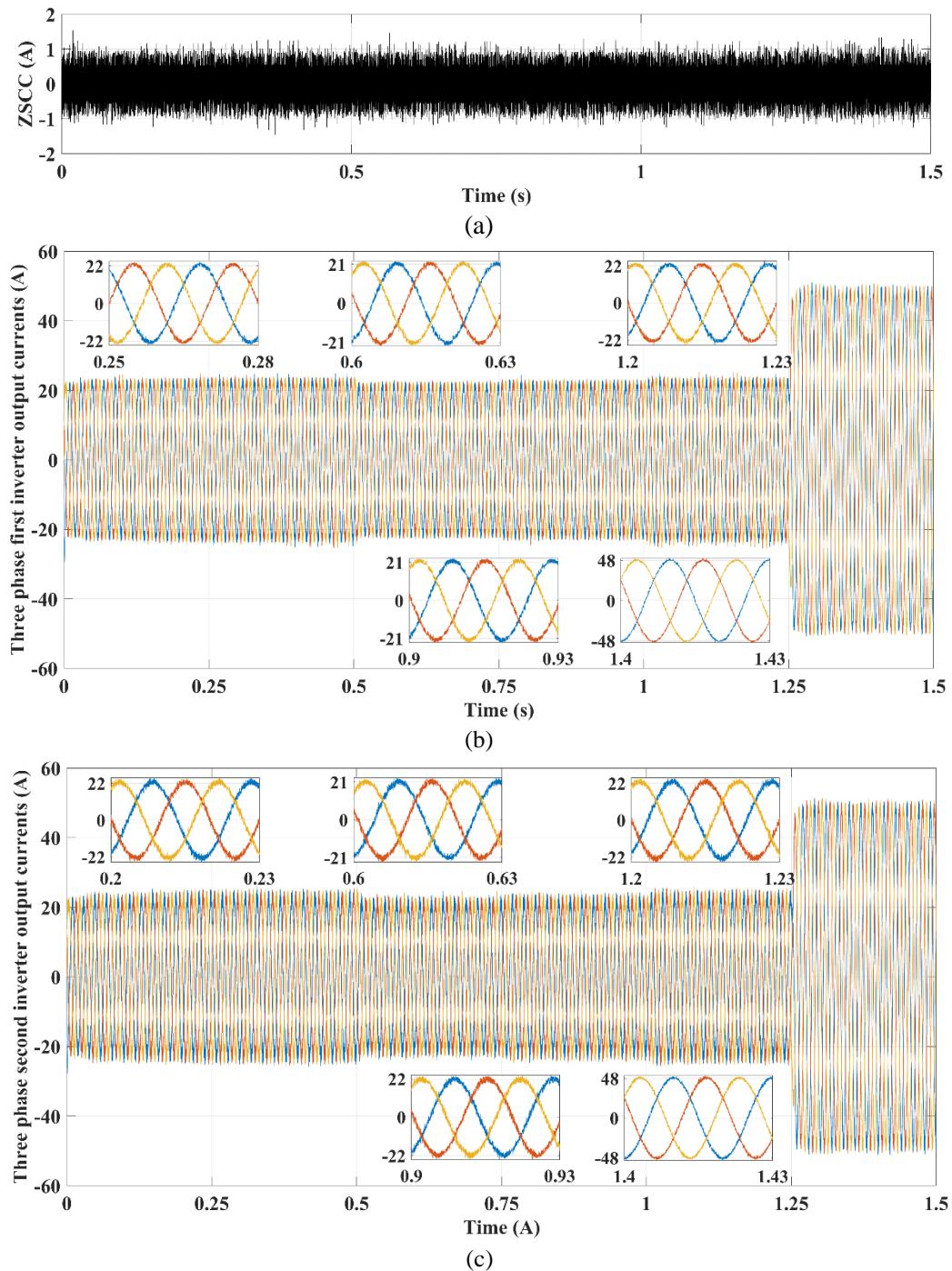

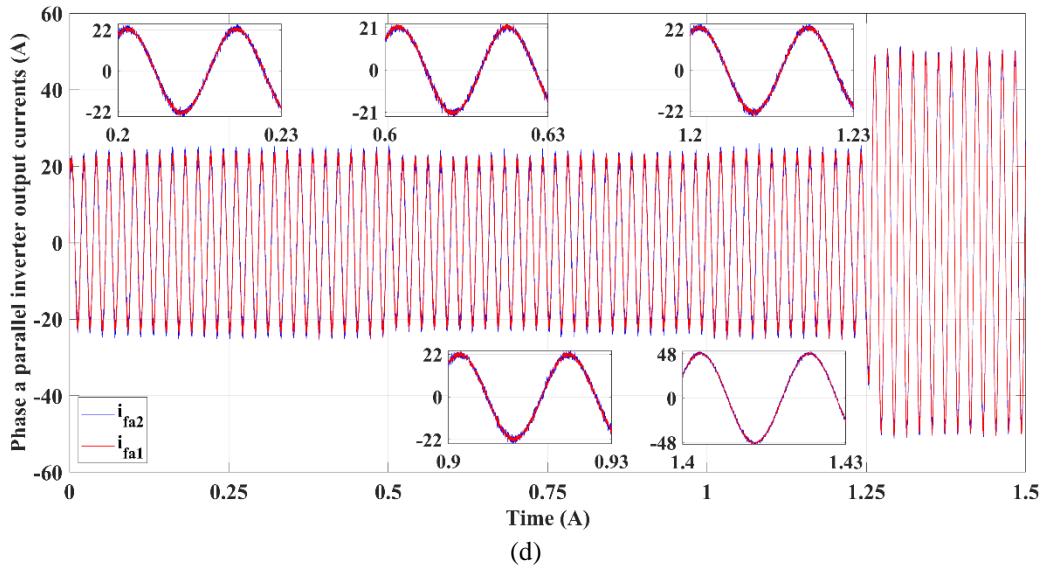

| Figure III.14        | Performance of the overall system controlled using the adjusted modulation voltage references based SPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-e)                                                                                                                          | 121-123     |

| Figure III.15        | Performance of the adjusted modulation voltage references based SPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-d)                                                                                                                                                              | 124-125     |

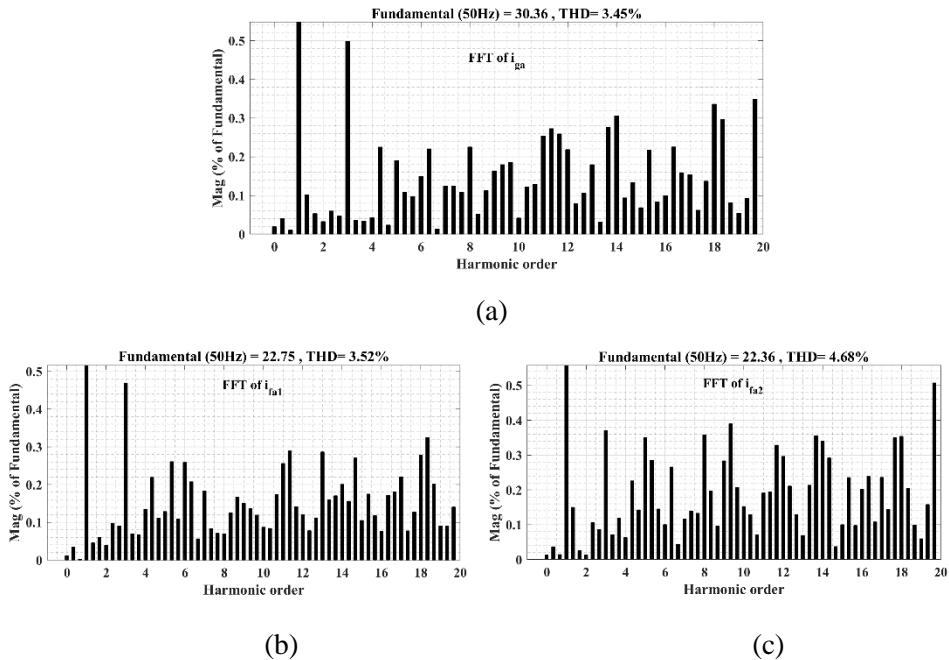

| Figure III.16        | Harmonic spectrums. (a) first phase grid current, (b) first phase of first 4LI output current, (c) first phase of second 4LI output current                                                                                                                                                                                          | 125         |

| Figure III.17        | Control block diagram of the PV parallel 4LI grid connected system based reactive power compensation using the proposed adjusted 3DSVPWM                                                                                                                                                                                             | 127         |

| Figure III.18        | Bloc diagram of the PI loop of ZSCC-based adjusted 3DSVPWM                                                                                                                                                                                                                                                                           | 128         |

| Figure III.19        | Performance of the overall system controlled using the adjusted 3DSVPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-e)                                                                                                                                                           | 129-131     |

| Figure III.20        | Performance of the adjusted 3DSVPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-d)                                                                                                                                                                                               | 131-133     |

| Figure IV.1          | Topologies of the PV grid connected parallel 4LI's system                                                                                                                                                                                                                                                                            | 140         |

| Figure IV.2          | Schematic diagram of the ADRC method-based outer DC bus voltage control loop                                                                                                                                                                                                                                                         | 145         |

| Figure IV.3          | Schematic diagram of the ADRC method-based inner output current control loop                                                                                                                                                                                                                                                         | 147         |

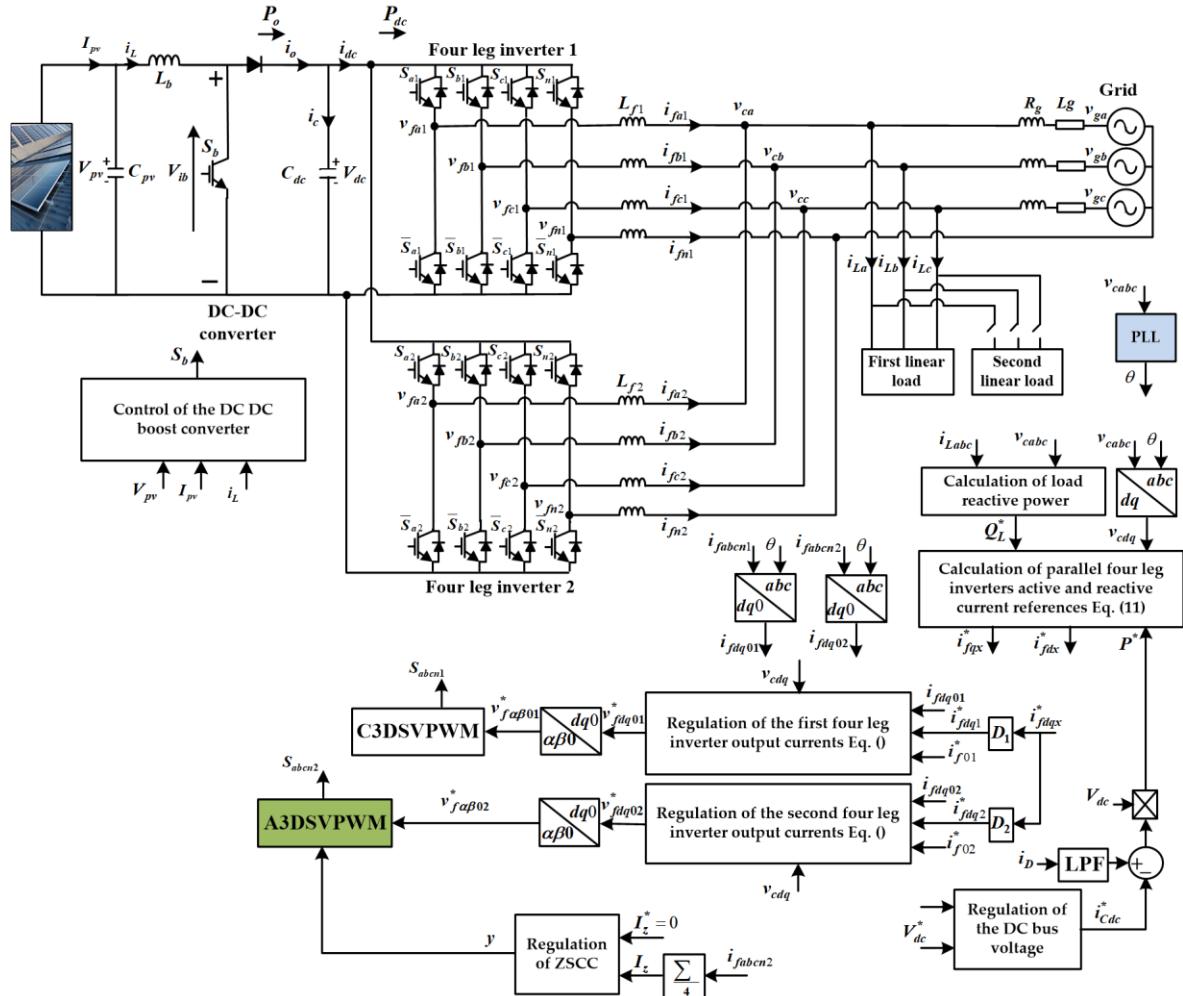

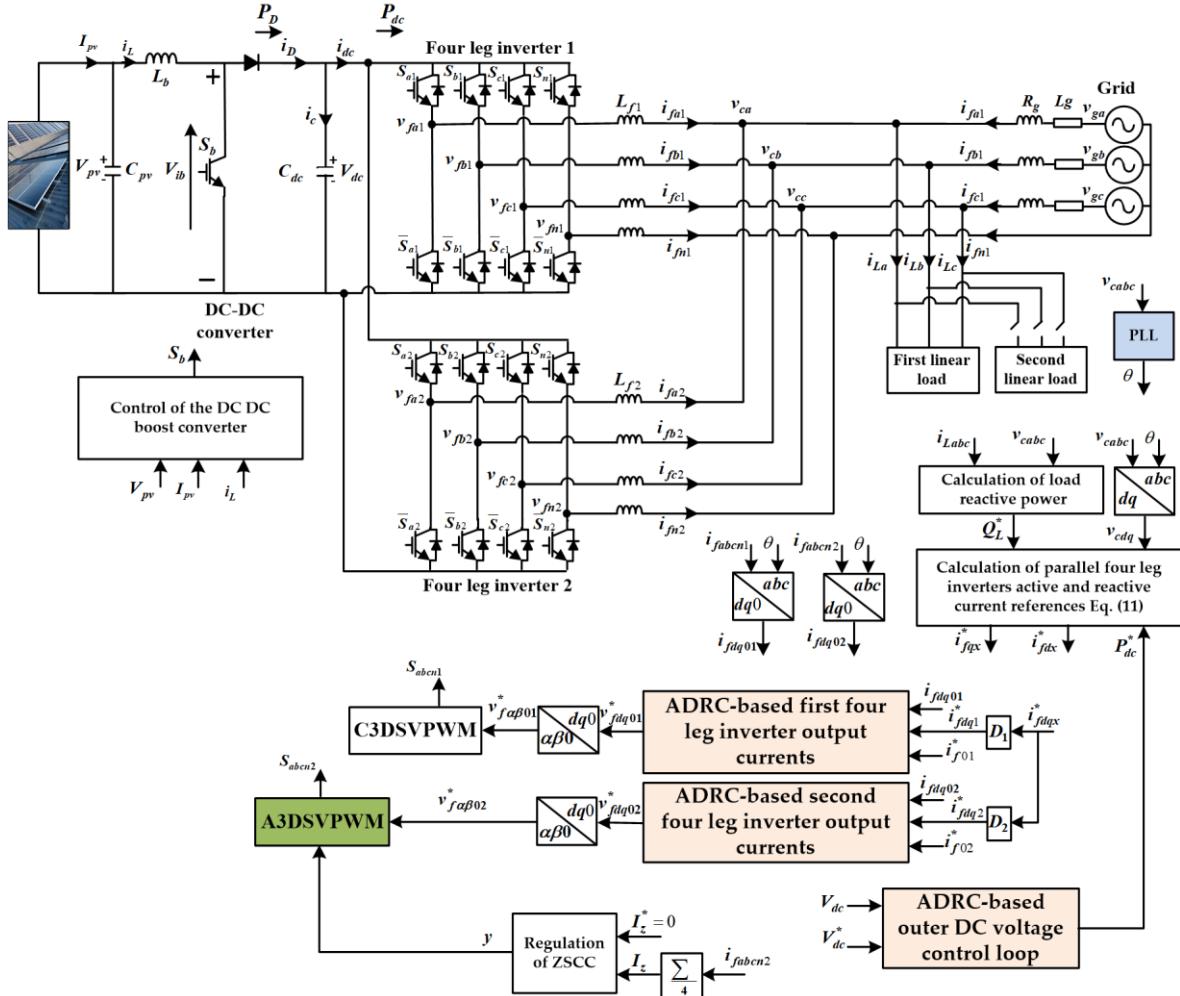

| Figure IV.4          | The overall control structure of the PV grid connected parallel 4LI's system controlled using ADRC method with adjusted 3D SVPWM                                                                                                                                                                                                     | 151         |

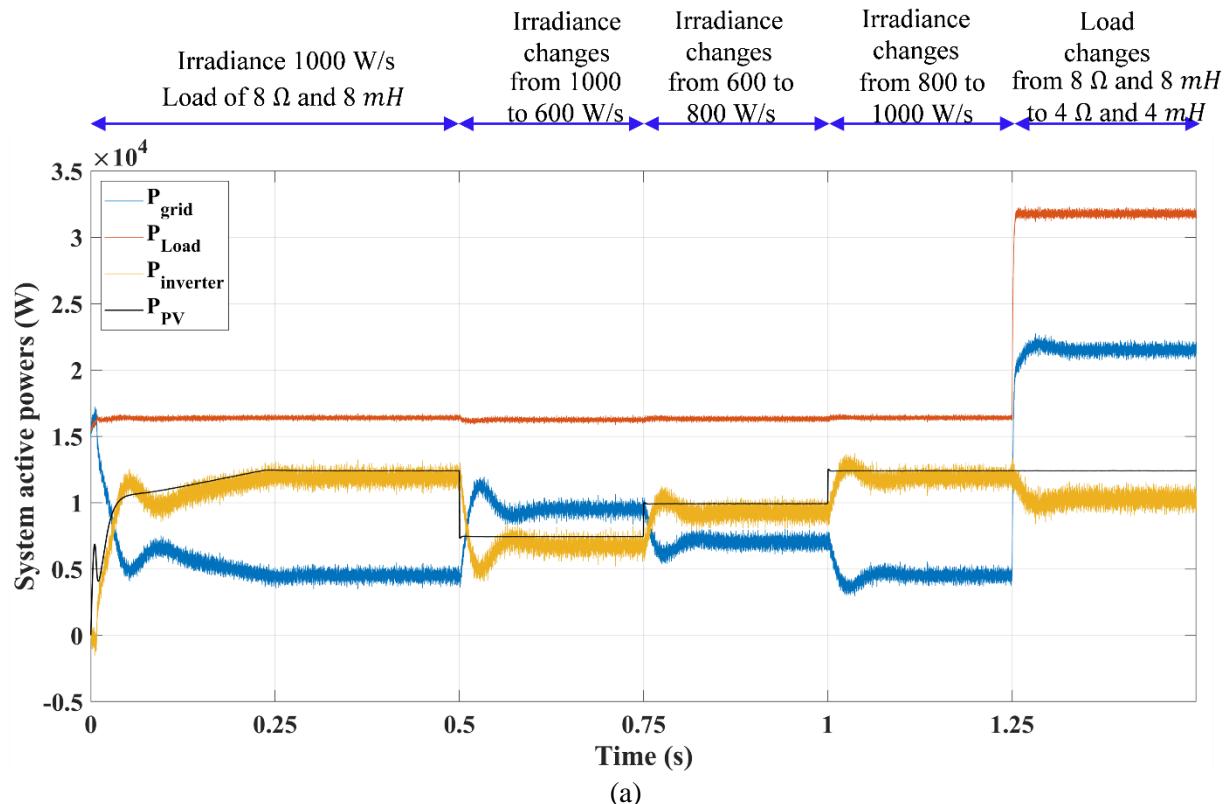

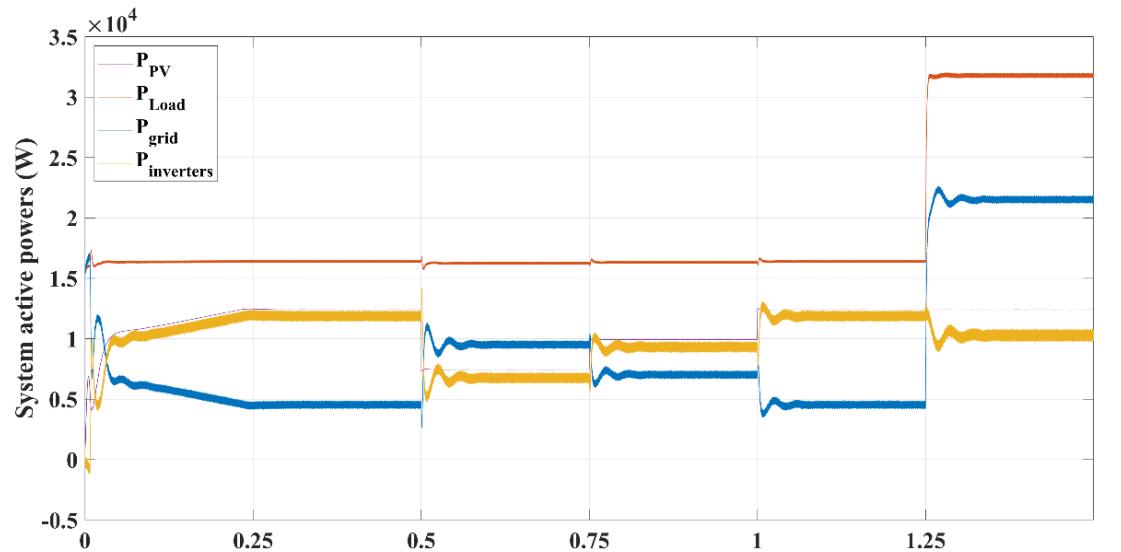

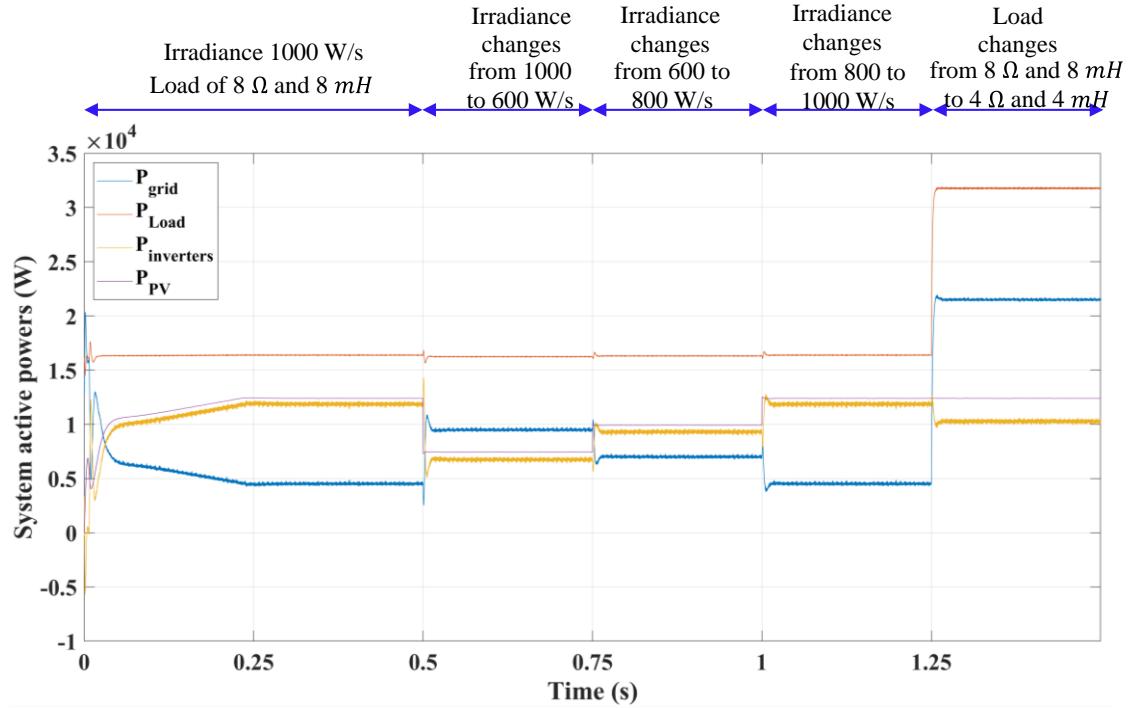

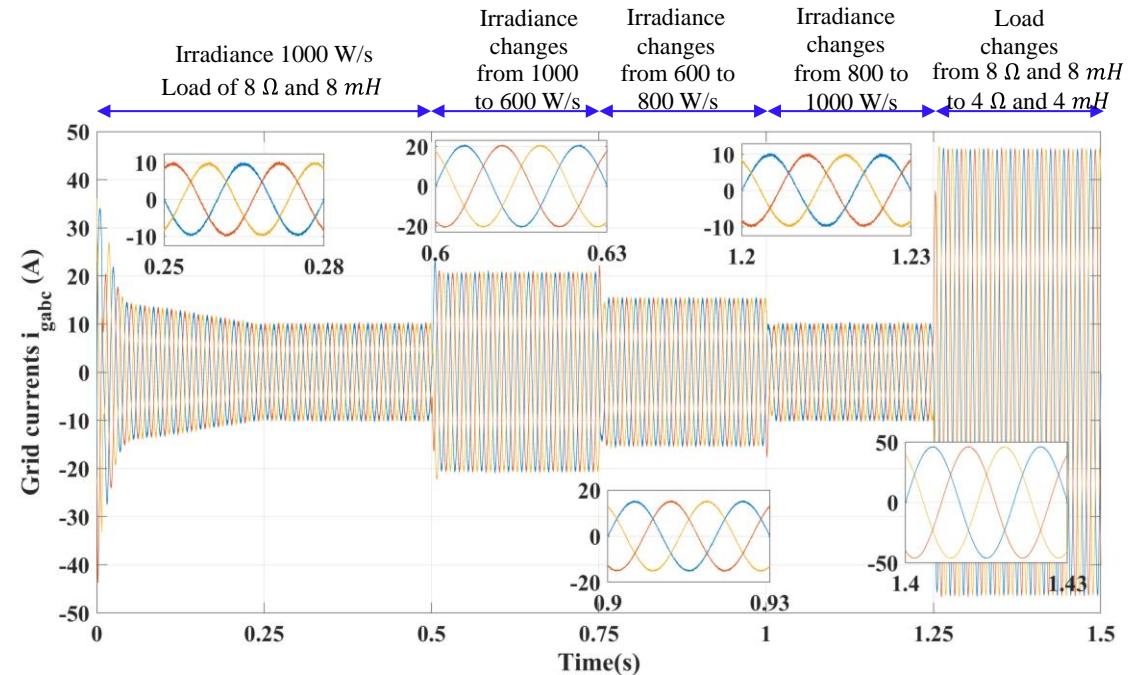

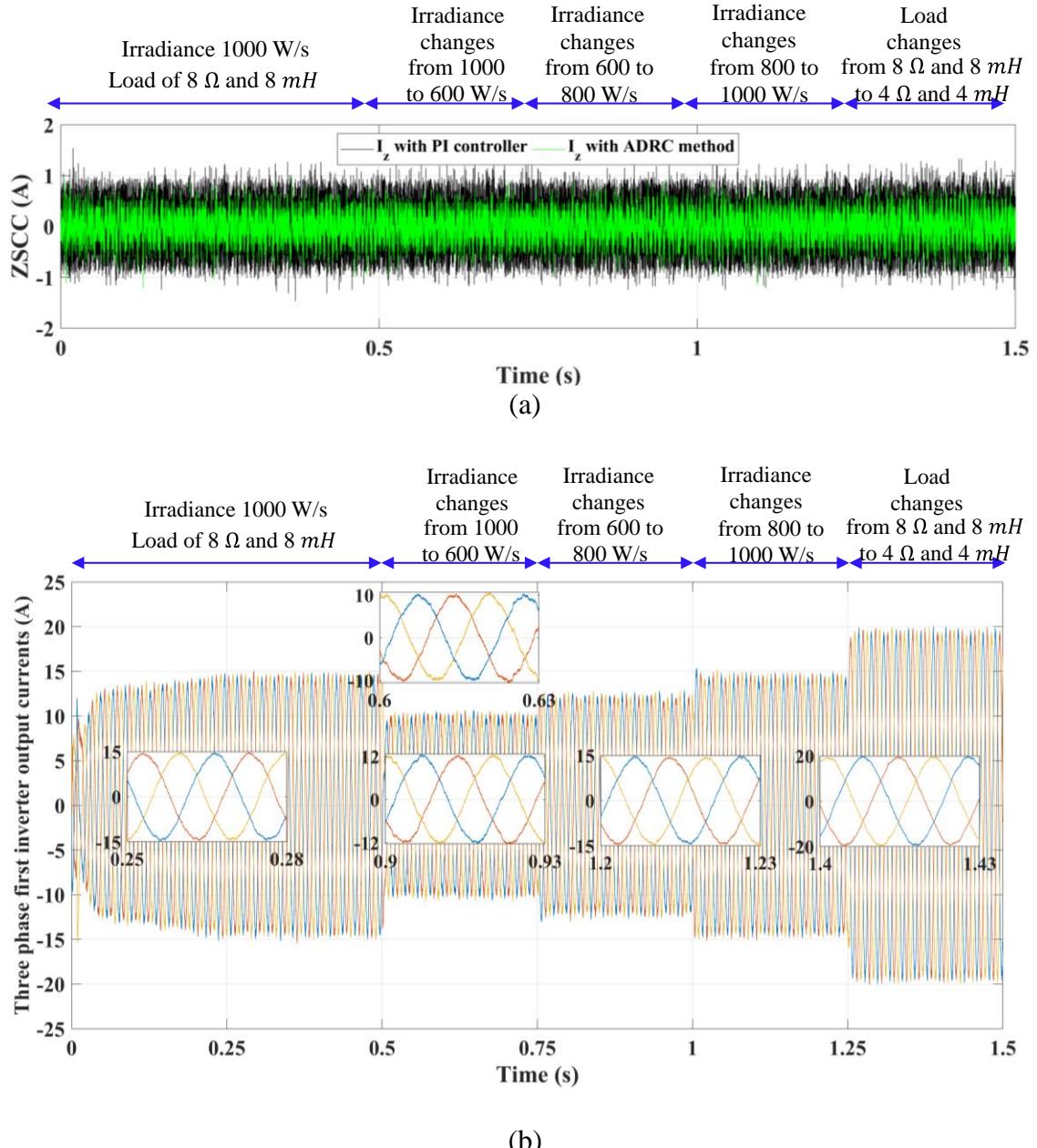

| Figure IV.5          | Performance of the overall system controlled using the ADRC method with adjusted 3DSVPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-e)                                                                                                                                          | 155-157     |

| Figure IV.6          | Harmonic spectrums of first phase grid current. (a) between 0 and 0.5s, (b) between 1.25 and 1.5s                                                                                                                                                                                                                                    | 157         |

| Figure IV.7          | Performance of the ADRC method with 3DSVPWM under unbalanced output filter inductances and the changes of irradiance and load (subfigures a-d)                                                                                                                                                                                       | 160-161     |

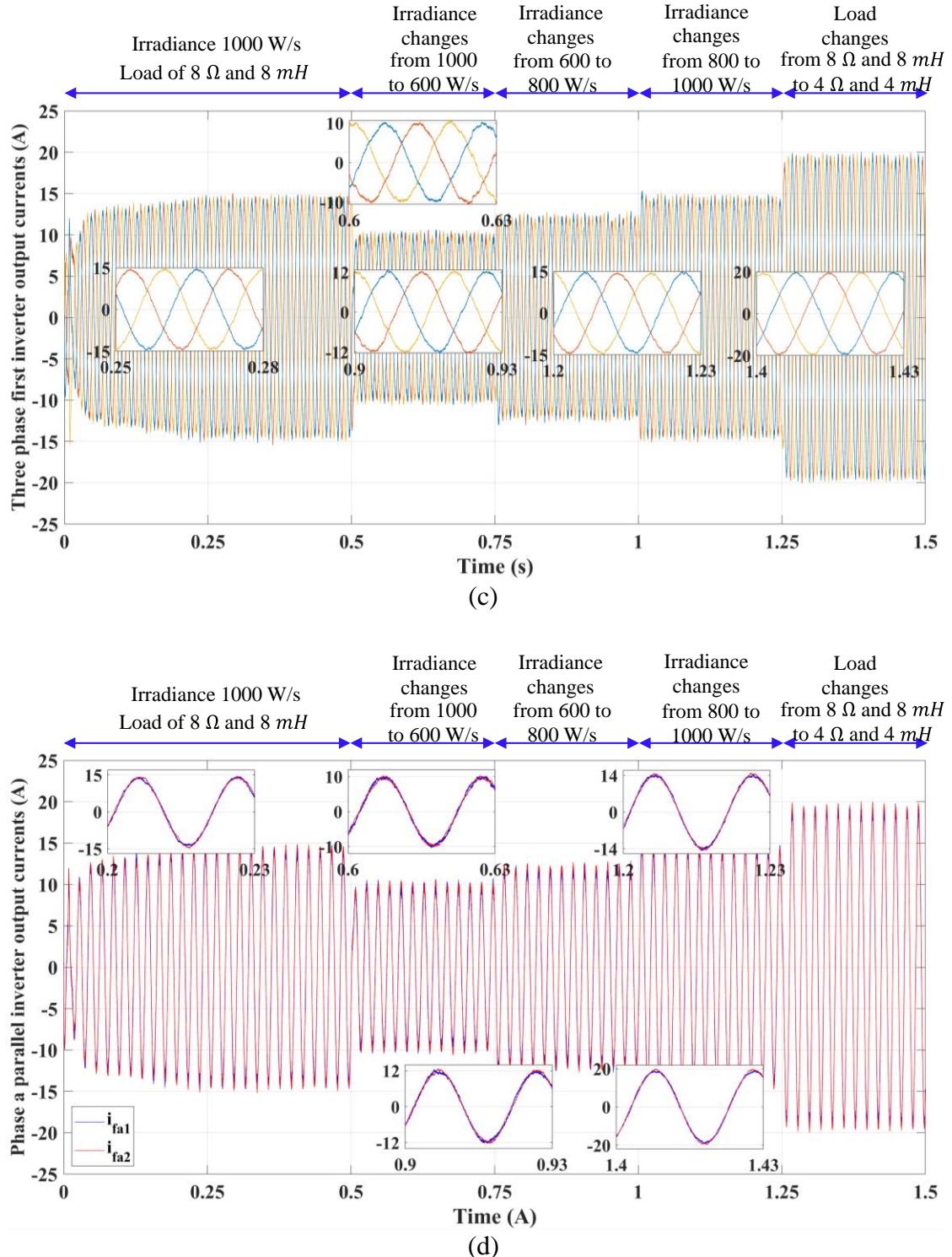

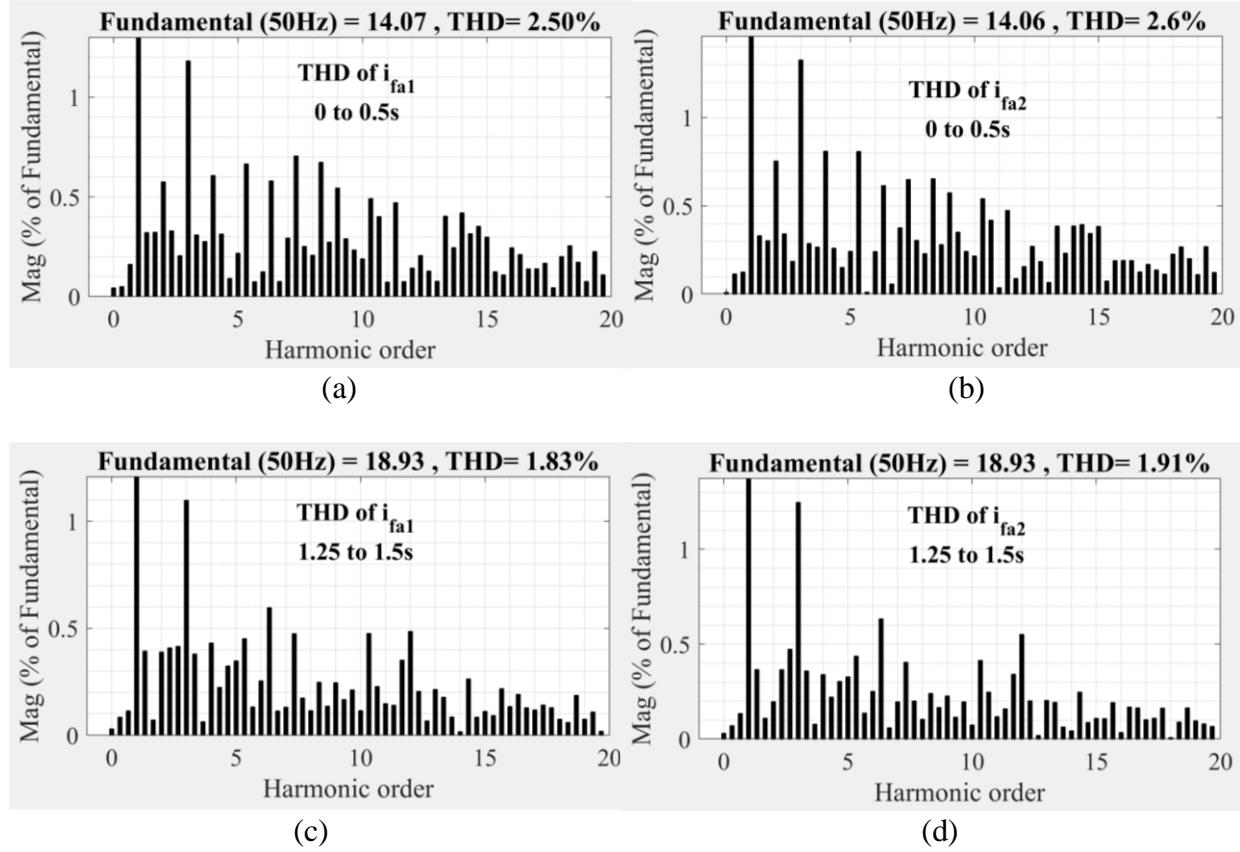

| Figure IV.8          | Harmonic spectrums of both 4LI's first phase output currents. (a) first phase output current of first 4LI between 0 and 0.5s, (b) first phase output current of second 4LI between 0 and 0.5s, (c) first phase output current of first 4LI between 1.25 and 1.5s, (d) first phase output current of second 4LI between 1.25 and 1.5s | 162         |

### List of Tables

|            |                                                                               |    |

|------------|-------------------------------------------------------------------------------|----|

| Table I.1  | Electrical Characteristics of the BP SX 150 PV Module                         | 26 |

| Table II.1 | Switching states and corresponding voltage vectors in the abc reference frame | 53 |

|             |                                                                                                                                   |       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

| Table II.2  | Switching states and corresponding voltage vectors in the ( $\alpha\beta0$ ) reference frame                                      | 54    |

| Table 2.3   | The three non-zero switching state vectors in each tetrahedron                                                                    | 76    |

| Table 2.4   | Equations of the planes delimiting each tetrahedron                                                                               | 79    |

| Table 2.5   | Projection matrix [A] for each tetrahedron to determine the duty cycles                                                           | 82-83 |

| Table III.1 | Comparison between the Adjusted SPWM (Test B) and the Proposed Adjusted 3D-SVPWM (Test C)                                         | 133   |

| Table IV.1  | Comparison between both the PI controller with Adjusted 3D-SVPWM in Chapter 3 and the proposed ADRC method with Adjusted 3D-SVPWM | 165   |

### Publications and communications under this Phd Thesis

- 1- Al-Dwa, A. A. M., Chebabhi, A., Ziane, D., Barkat, S., Ihammouchen, S., Rekioua, T., Alhejji, A. Real-time implementation of a new modified 3DSVPWM control method for eliminating zero-sequence circulating current in parallel three-phase four-leg source voltage inverters. *IEEE Access*, 12, 101121-101138, 2024

- 2- Chebabhi, A., Al-dwa, A. A. M., Defdaf, M., Kessal, A. New modeling and enhanced control strategy for grid-connected four-leg inverter without phase-locked loop and park's transformation. *Revue Roumaine des Sciences Techniques—Serie Électrotechnique et Énergétique*, 68(2), 121-126, 2023.

- 3- Al-Dwa, A. A. M., Chebabhi, A., Defdaf, M., Guessabi, A. New Modeling and Improved Current Control Strategy to Eliminate the Impact of Synchronization Method and Parks Transformation for Grid-connected Four-leg PWM Inverter. *Periodica Polytechnica Electrical Engineering and Computer Science*, 67(2), 204-215, 2023

- 4- Al-Dwa, A. A. M., Ali, C., Adel, C., Said, B., Karim, F. M. Modified carrier-based SPWM technique for zero sequence circulating current elimination in parallel inverters. In *2022 IEEE International Conference of Advanced Technology in Electronic and Electrical Engineering (ICATEEE)*, Msila, November 2022.

## TABLE OF CONTENTS

|                                                                                                              |             |

|--------------------------------------------------------------------------------------------------------------|-------------|

| <b>CERTIFICATE OF ORIGINAL AUTHORSHIP</b>                                                                    | <b>ii</b>   |

| <b>ACKNOWLEDGEMENTS</b>                                                                                      | <b>iii</b>  |

| <b>Abstract</b>                                                                                              | <b>iv</b>   |

| <b>TABLE OF CONTENTS</b>                                                                                     | <b>vi</b>   |

| <b>List of Abbreviations</b>                                                                                 | <b>x</b>    |

| <b>List of Figures</b>                                                                                       | <b>xiii</b> |

| <b>List of Tables</b>                                                                                        | <b>xv</b>   |

| <b>Chapter 1: Overview of PV Systems for Grid-Connected Application and Power Quality Improvement</b>        |             |

| I.1. Introduction                                                                                            | 7           |

| I.2. Overview of Semiconductors                                                                              | 8           |

| I.2.1. Structure of a PN Diode                                                                               | 8           |

| I.2.2. I-V Characteristics of the PN Diode                                                                   | 8           |

| I.2.3. Light Absorption                                                                                      | 8           |

| I.2.4. Electron-Hole Pairs                                                                                   | 9           |

| I.3. Photovoltaic Cells                                                                                      | 9           |

| I.3.1. The PV Cell Working Principle                                                                         | 10          |

| I.3.2. Type of PV Cell                                                                                       | 10          |

| I.3.3. Mathematical Modeling of PV Module                                                                    | 13          |

| I.3.3.1. Two-Diode Model                                                                                     | 13          |

| I.3.3.2. Single-Diode Model                                                                                  | 15          |

| I.3.4. Model including Ohmic Losses                                                                          | 17          |

| I.3.4.1. Current-Based Model                                                                                 | 17          |

| I.3.4.2. Voltage-Based Model                                                                                 | 17          |

| I.3.5. Calculation of Cell Current Under Standard Reference Conditions of Temperature Tref and Irradiance G0 | 18          |

| I.3.5.1. Calculation of Saturation Current at Tref =298K                                                     | 18          |

| I.3.5.2. Calculation of Series Resistance at Tref                                                            | 18          |

| I.3.6. Calculation of Cell Current at any Temperature T and Irradiance G                                     | 19          |

| I.3.6.1. Calculation of Short-Circuit Current at Any Temperature and Irradiance                              | 19          |

| I.3.6.2. Calculation of Saturation Current at Any Temperature                                                | 20          |

| I.3.7. Characteristics of a PV Cell                                                                          | 20          |

| I.3.7.1. Open-Circuit Voltage                                                                                | 21          |

| I.3.7.2. Short-Circuit Current                                                                               | 21          |

| I.3.7.3. Power-Voltage Characteristic                                                                        | 21          |

| I.3.7.4. Fill Factor of a PV Cell                                                                            | 22          |

| I.3.7.5. Efficiency                                                                                          | 22          |

| I.3.8. Connection of Cells                                                                                   | 22          |

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| I.3.8.1. Series Connection of Cells                                                      | 22 |

| I.3.8.2. Parallel Connection of Cells                                                    | 22 |

| I.3.8.3. Series-Parallel Connection of Cells (PV Array)                                  | 23 |

| I.4. Photovoltaic Module (Panel)                                                         | 23 |

| I.4.1. Modeling of Photovoltaic Module                                                   | 24 |

| I.4.1.1. Current Model                                                                   | 24 |

| I.4.1.2. Voltage Model                                                                   | 24 |

| I.5. Electrical Characteristics of a PV Module                                           | 25 |

| I.5.1. Effect of Solar Irradiance on $I_{sc\_Module}$ , $V_{oc\_Module}$ , and $P_{max}$ | 26 |

| I.5.2. Effect of Temperature on $I_{sc\_Module}$ , $V_{oc\_Module}$ , and $P_{max}$      | 27 |

| I.5.3. Impact of Series Resistance                                                       | 27 |

| I.5.4. Partial shading influence on PV system's electrical characteristics               | 28 |

| I.6. Photovoltaic Generator structure and Modeling                                       | 28 |

| I.6.1. Structure of a PV Generator                                                       | 28 |

| I.6.2. Modeling of a PV Generator                                                        | 29 |

| I.6.2.1. PVG current model                                                               | 29 |

| I.6.2.2. PVG voltage model                                                               | 30 |

| I.7. PVG-based standalone power supply system                                            | 30 |

| I.7.1. DC-DC Converters                                                                  | 31 |

| I.7.2. Types of DC-DC Converters                                                         | 31 |

| I.7.2.1. Boost Converter                                                                 | 32 |

| I.7.2.2. Operating Principle of a boost converter                                        | 32 |

| I.7.2.3. Operation in Continuous Conduction Mode (CCM)                                   | 33 |

| I.7.2.3.1. Calculation of the input inductance value in CCM                              | 34 |

| I.7.2.3.2. Inductor current ripple                                                       | 36 |

| I.7.2.3.3. Output DC voltage ripple                                                      | 36 |

| I.7.2.4. Sizing of DC-DC boost converter components                                      | 37 |

| I.7.2.4.1. Sizing of DC-DC boost converter's input inductor                              | 37 |

| I.7.2.4.2. Sizing of DC-DC boost converter's output capacitor                            | 37 |

| I.7.2.4.3. Sizing of DC-DC boost converter's input capacitor                             | 38 |

| I.8. Pulse Width Modulation (PWM) Principle                                              | 38 |

| I.9. Maximum Power Point Tracking Algorithms                                             | 38 |

| I.9.1. Perturb And Observe                                                               | 39 |

| I.9.2. Incremental Conductance                                                           | 40 |

| I.9.3. Sliding Mode MPPT Algorithm                                                       | 41 |

| I.9.4. Artificial Neural Network MPPT                                                    | 42 |

| I.9.5. Fuzzy Logic Controller                                                            | 42 |

| I.9.6. Meta-Heuristic and Bio-Inspired Techniques                                        | 43 |

| I.10. Linear Control of the Boost Converter                                              | 45 |

| I.10.1. Synthesis of the PI controller for the PVG output voltage                        | 46 |

| I.10.2. Synthesis of the PI controller for input inductor current                        | 47 |

| I.11. Conclusion                                                                         | 48 |

## Chapter 2: Modeling and control of PVG four leg inverter in the grid connected system

|                                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------|----|

| II.1. Introduction                                                                                             | 50 |

| II.2. Modeling and operating principle of the 4LI                                                              | 51 |

| II.2.1. Operating principle of the 4LI                                                                         | 51 |

| II.2.1.1. Output voltages of the 4LI                                                                           | 51 |

| II.2.1.2. Representation Vectorial of the 4LI                                                                  | 53 |

| II.3. Description and Modeling of a PVG Grid-Connected 4LI                                                     | 55 |

| II.3.1. Modelling of the PVG grid connected 4LI                                                                | 56 |

| II.3.1.1. Model of the PVG                                                                                     | 56 |

| II.3.1.2. Model of the grid connected 4LI                                                                      | 56 |

| II.3.1.2.1. Four leg inverter output current dynamics                                                          | 56 |

| II.3.1.2.2. DC bus voltage dynamic                                                                             | 58 |

| II.3.1.2.3. Relationship between AC and DC sides of the 4LI                                                    | 59 |

| II.3.1.3. Sizing of 4LI's input and output passive filters                                                     | 60 |

| II.3.1.3.1. Sizing of 4LI's input DC capacitor                                                                 | 60 |

| II.3.1.3.2. Sizing of 4LI's output filter inductor                                                             | 61 |